TOSHIBA BI-CMOS Integrated Circuit

## **TB62718AF**

#### Controller and Driver for Full-color LED Modules and Panels

The TB62718AF is an LED driver which is suitable for driving full-color LED modules. This device has built-in 8 bit PWM grayscale and an output current adjustment functions. It can turn on to 16 LEDs. This device has a heat sink fitting side on the surface of the package. Then, a heat sink will dissipate heat generated in the device. In addition, this device incorporates built-in TSD (thermal Shutdown) and output-open detection functions to protect the device.

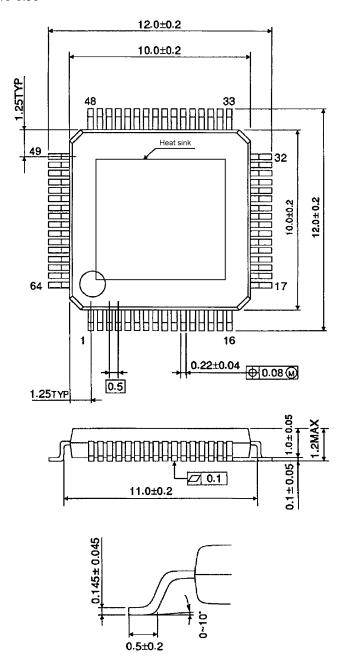

Weight: 0.26 g (typ.)

#### **Features**

- Output current capability and number of outputs: 90 mA × 16 outputs

- Constant current range: 5 mA~75 mA

- Application output voltage: 0.7 V (output current 5 mA~90 mA)

- Adjustment function

- 1. Standard current adjustment (8-bit serial data input)

This function supports standard current adjustment using an external resistance connected to the REXT pin.

- 2 high-order bits

- ... Output current can be adjusted to any one of 4 levels in the range 25%~100%.

- 6 low-order bits

- ... Output current can be adjusted to any one of 64 levels in the range 40%~100%.

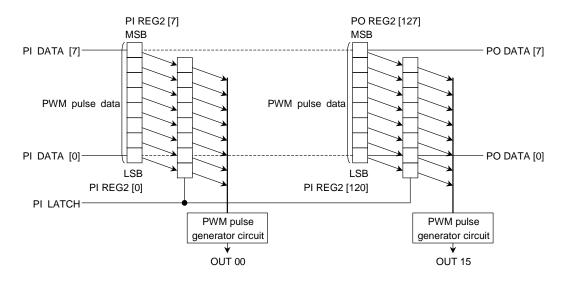

- 2. Each dot adjustment (128-bit serial data input)

This function allows adjustment of the current value for each output (dot).

- ... Output current can be adjusted to any one of 64 levels in the range 20%~100%.

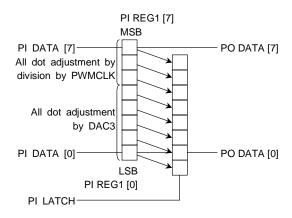

- 3. All dot adjustment 1 (8-bit parallel data input)

This function allows adjustment of brightness for each LED module.

5 low-order bits ... Output current can be adjusted to any one of 32 levels in the range 50%~100%.

4. All dot adjustment 2 (8-bit parallel data input)

This function allows changes to the frequency of the PWM clock and allows major brightness adjustment for the display.

3 high-order bits ... PWM clock frequency can be adjusted to any one of 8 levels in the range 1/1~1/8.

5. 256-grayscale PWM function (8-bit parallel input)

This function controls the pulse width for each output, yielding 256 grayscales.

Maximum PWM clock frequency 10 MHz (for all temperature range), Minimum pulse width 2 ms

1

- · Accuracy of bits in constant-current output levels prior to adjustment

- ±6.0% max (for output current of 40 mA~80 mA)

- ±7.0% max (for output current of 20 mA~40 mA)

- ±12.0% max (for output current of 5 mA~20 mA)

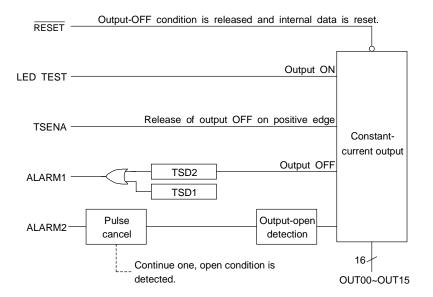

- Protection functions

- 1. Thermal shutdown function (TSD)

This function monitors the rise in junction temperature.

Connect a pull-up resistor to the ALARM1 pin in order to monitor the temperature.

2. Output Pin Open Detection function

This function detect when an output pin is open.

Connect a pull-up resistor to the ALARM2 pin in order to monitor this.

- For anode-common LEDs

- Input signal voltage level: CMOS level (Schmitt trigger input)

- Power supply voltage range  $V_{DD} = 4.5 \text{ V} \sim 5.5 \text{ V}$

- Maximum output pin voltage: 26 V

- Serial and parallel data transfer rate: 20 MHz (max, cascade connection)

- Operating temperature range T<sub>opr</sub> = −40°C~85°C

- Package: HQFP64-P-1010-0.50. A Heat sink can be fitted.

## Warnings

Short-circuiting an output pin to GND or to the power supply pin may destroy the device. Take care when wiring the output pins, the power supply pin and the GND pins ( $V_{SS}$ ,  $V_{SS2}$ ). Do not apply either positive or negative voltages to the heat sink on the surface of the IC. In addition, do not solder anything to the heat sink.

2 2006-06-14

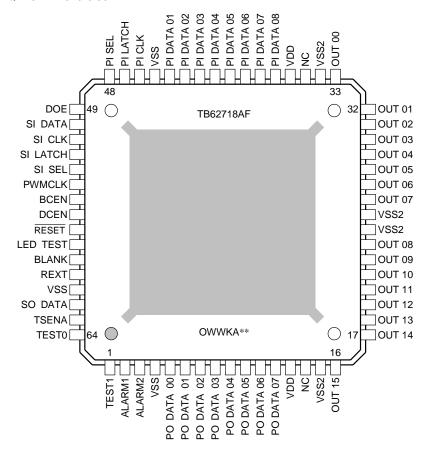

## Pin Assignment (top view) and Markings

Package type: HQFP64-P-1010-0.50

Note: Indicates device name on the upper surface of the package. Indicates weekly code on the lower surface of the package.

Details of weekly code on lower surface:

From left,

1st character = rightmost digit of year 0 for 2000, 1 for 2001

2nd and 3rd characters = week of manufacture during year: maximum value = 52.

4th characters = manufacturing factory ('K' means the Kita Kyushu factory.)

5th to 7th characters = lot number within week

1st lot is A11, 2nd lot is A1 and 3rd lot is A.

4th lot is B11, 5th lot is B1 and 6th lot is B.

64th lot is Z11, 65th lot is Z1 and 66th lot is Z.

The four characters of 'I', 'M', 'O' and 'W' are not used.

3 2006-06-14

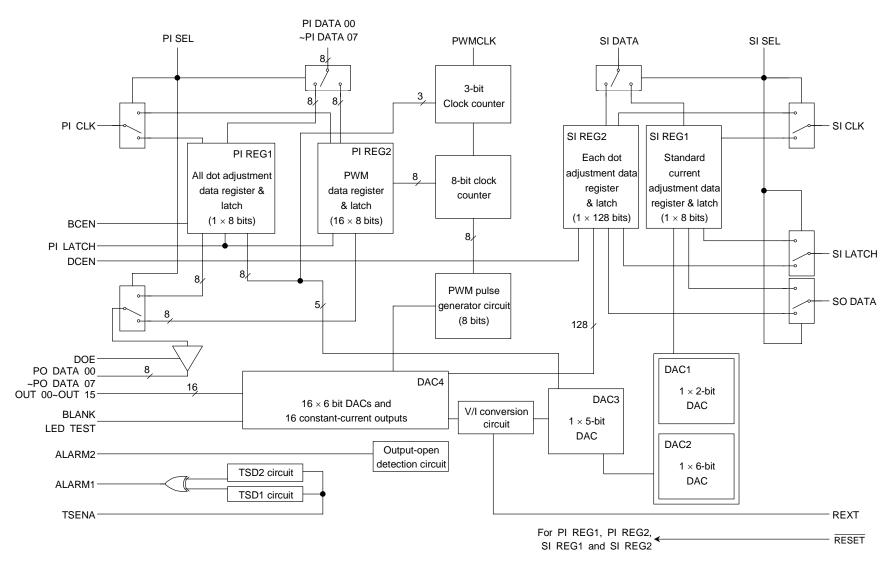

## **Block Diagram (entire device)**

4

2006-06-14

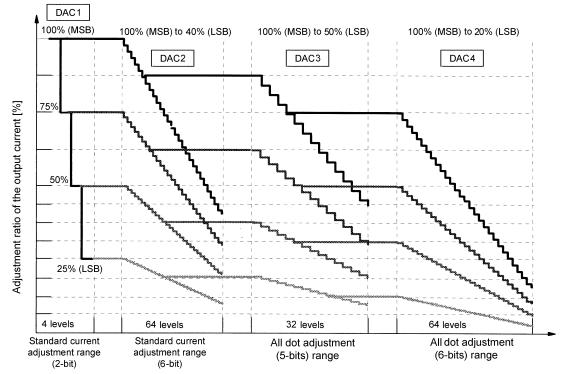

## **Constant Current Adjustment Range (graph)**

This graph shows how current may be adjusted to a fraction of its full-scale value.

All dot adjustment

Note 1: In each case, the value input to each DAC is the value output from the previous DAC.

Reference: Current adjustment functions

DAC1 to DAC3 are the current adjustment functions for all outputs.

The adjustment width of DAC1 is large and approximate (1 LSB  $\simeq$  25%).

The adjustment width of DAC2 is the smallest and has a large error (1 LSB  $\simeq$  0.9%).

The adjustment width of DAC3 is small. DAC3 is a high-performance DAC with a small error (1 LSB  $\approx$  1.61%).

Therefore.

It is recommended that DAC1 and DAC2 be used for adjusting the REXT resistance.

It is recommended that DAC3 be used for adjusting brightness between module.

(after it was set and it had DAC4 adjusted to the dot.)

The beginning is set in about 75% of the middle value, after that, it is effective to use  $\pm 25\%$  of set width.

DAC4 is the current adjustment function for all outputs.

The adjustment width of DAC4 is small. But it is a high-performance DAC with a small error (1 LSB  $\simeq$  1.27%).

And also, DAC4 has a very wide setting range.

Therefore, DAC4 can be used to adjust the brightness of LEDs without a rank classification. This method allows brightness to be adjusted with a degree of accuracy of 1.27% of full scale.

Note 2: Assuming precise linear correlation between output current and LED brightness

## **Equivalent Input and Output Circuits (resistance values are typical values.)**

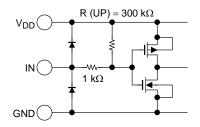

## Input pins with pull-up resistor TSENA, BLANK, BC/DCEN

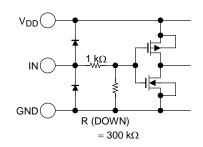

#### Input pins with pull-down resistor.

SI/PI LATCH, PI DATA 00~PI DATA 07, LED TEST

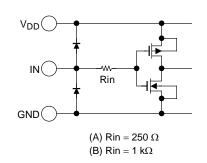

## Input terminals

(A) SI DATA, SI CLK, PI CLK, PWMCLK (B)  $\overline{\text{RESET}}$ ,  $\overline{\text{DOE}}$ , PI SEL, SI SEL

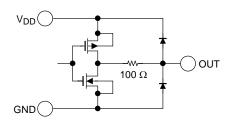

### **Output terminals**

PO DATA 00~PO DATA 07, SO DATA

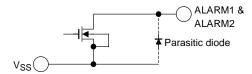

#### **Protection circuit monitor terminals**

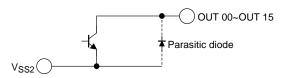

### **Constant-current output terminals**

## **Explanation of Pin Functions Table**

| No.               | Name                      | I/O |               | Function Explanation                                                                                                                                                                                                                                                                        |

|-------------------|---------------------------|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 45             | VSS                       | Р   | _             | Logic ground pins. Be sure to use all.                                                                                                                                                                                                                                                      |

| 35, 14            | NC                        | _   | _             | Unused                                                                                                                                                                                                                                                                                      |

| 63                | TSENA                     | 1   | Pull-<br>up   | This pin is used to reset the IC's built-in temperature monitoring circuit (TSD). Rising edge of input signal re-enables outputs which had been forced to OFF. The latched data as the setting is not reset. Either in case of H- or L-level of this terminals can be operated TSD circuit. |

| 15, 24,<br>25, 34 | VSS2                      | Р   | _             | Ground pin for output. Be sure to use all.                                                                                                                                                                                                                                                  |

| 13, 36            | VDD                       | Р   | _             | Logic power supply input pins. Be sure to use all.                                                                                                                                                                                                                                          |

| 16~23,<br>26~33   | OUT 00~<br>OUT 15         | 0   | _             | LED drive output pins. Connect to cathode of LED.                                                                                                                                                                                                                                           |

| 50                | SI DATA                   | 1   | _             | Serial data input pin. Used for input of standard current adjustment data and dot adjustment data                                                                                                                                                                                           |

| 51                | SI CLK                    | ı   | _             | Serial data transfer clock input pin. Data is transferred positive edge.                                                                                                                                                                                                                    |

| 52                | SI LATCH                  | I   | Pull-<br>down | Serial data latch signal input pin. Data is held on positive edge.                                                                                                                                                                                                                          |

| 53                | SI SEL                    | ı   | _             | Serial data selection pin. Either standard current adjustment data or dot adjustment data may be selected.                                                                                                                                                                                  |

| 62                | SO DATA                   | 0   | _             | Serial data output pin. The output data type is selected using SI SEL.                                                                                                                                                                                                                      |

| 37~44             | PI DATA 00~<br>PI DATA 07 | 1   | Pull-<br>down | Input pins for parallel data. Inputs for all output adjustment data and PWM data                                                                                                                                                                                                            |

| 46                | PI CLK                    | ı   | _             | Input pin for parallel data transfer clock. Data is transferred on positive edge.                                                                                                                                                                                                           |

| 47                | PI LATCH                  | -   | Pull-<br>down | Input pin for parallel data latch signal. Data is held on rising positive edge.                                                                                                                                                                                                             |

| 48                | PI SEL                    | -   | _             | Parallel data selection pin. Either all output adjustment data or PWM data may be selected.                                                                                                                                                                                                 |

| 5~12              | PO DATA 00~<br>PO DATA 07 | 0   | _             | Output pin for parallel data. The output data type is selected using PISEL.                                                                                                                                                                                                                 |

| 49                | DOE                       | 1   | _             | Control pin for parallel data output PODATA. PIDATA is out on input of an H-level signal. PIDATA is set to High-impedance by input of an L-level signal.                                                                                                                                    |

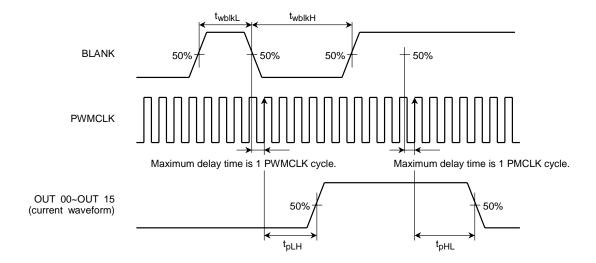

| 59                | BLANK                     | I   | Pull-<br>up   | PWM circuit control signal input pin. Output is turn OFF by input of an H-level signal. PWM output is initiated by input of an L-level signal accordingly to the input data.                                                                                                                |

| 54                | PWMCLK                    | -   | _             | Standard clock input pin for PWM circuit. One clock cycle is equivalent to the minimum pulse width of the PWM output.                                                                                                                                                                       |

| 55                | BCEN                      | 1   | Pull-<br>up   | Selection signal input pin for all output adjustment functions. All output adjustment is fixed to 100% when this signal is Low. All bit adjustments become effective when it is High. It isn't influent anything to all output adjustment by PWMCLK.                                        |

| 56                | DCEN                      | 1   | Pull-<br>up   | Selection signal input pin for dot adjustment function. Dot adjustment value is fixed to 100% when this signal is Low. Dot adjustment becomes effective when it is High.                                                                                                                    |

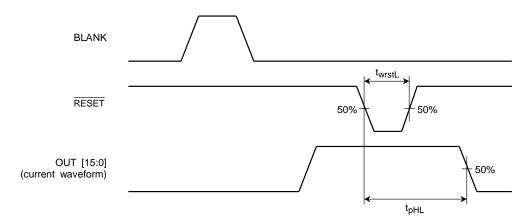

| 57                | RESET                     | ı   | _             | Reset signal input pin. Setting and registered data are reset when it is Low. A reset also releases TSD.                                                                                                                                                                                    |

| 58                | LED TEST                  | I   | Pull-<br>down | Connection confirmation signal input pin for an LED. When this signal is High, all outputs are ON. This signal should normally be kept Low.                                                                                                                                                 |

| 60                | REXT                      | Р   | _             | Connection pin of resistor for setting for the current.                                                                                                                                                                                                                                     |

| 2                 | ALARM1                    | 0   | _             | Open-drain monitor pin for TSD circuit. When the TSD circuit detects an abnormal temperature, this signal is turned ON. IO monitor the TSD circuit connect this pin to a pull-up resistor. ALARM1 is independent of the RESET signal.                                                       |

| 3                 | ALARM2                    | 0   | _             | Open-drain monitor pin for output-open detection circuit. When an open output is detected, this signal is turned ON.                                                                                                                                                                        |

| 1, 64             | TEST 0,<br>TEST 1         | I   | _             | Pins for the device testing. Connect all these pins to ground.                                                                                                                                                                                                                              |

Pin attributes P: power supply/ground/other, I: input pin, O: output pin

Note 3: It is recommended that pins with pull-up or pull-down resistors not be left open.

Ambient noise may cause malfunction of the device.

## Absolute Maximum Ratings (Topr = 25°C unless otherwise specified)

|                                | Characteristics                        | Symbol            | Rating                      | Unit   |

|--------------------------------|----------------------------------------|-------------------|-----------------------------|--------|

| Supply voltage                 |                                        | $V_{DD}$          | -0.3~7                      | V      |

| Constant-current o             | utput voltage                          | Vo                | -0.3~26                     | V      |

| Output current                 |                                        | lout              | 90                          | mA/bit |

| Logic output voltag            | е                                      | V <sub>OUT</sub>  | −0.3~ V <sub>DD</sub> + 0.3 | V      |

| Logic input voltage            |                                        | V <sub>IN</sub>   | -0.3~V <sub>DD</sub> + 0.3  | V      |

| Total V <sub>SS2</sub> current | (Note 5)                               | IV <sub>SS2</sub> | 1.44                        | Α      |

| Dower dissipation              | When device mounted on PCB (Note 6)    | P <sub>d</sub>    | 1.19                        | W      |

| Power dissipation              | When device mounted on PCB of any size | (Note 4)          | 5.0                         | VV     |

| Saturation heat                | When device mounted on PCB (Note 6)    | θ (j-a)           | 102                         | 0000   |

| resistance of<br>package       | When device mounted on PCB of any size | θ (j-c)           | 25                          | °C/W   |

| Operating tempera              | ture                                   | T <sub>opr</sub>  | -40~85                      | °C     |

| Storage temperatu              | re                                     | T <sub>stg</sub>  | -55~150                     | °C     |

Note 4: If the operating temperature exceeds 25°C, derate the power dissipation rating by 0.95 mW/°C.

Note 5: All four VSS2 pins must be connected. If not, device characteristics cannot be guaranteed.

Note 6: When device mounted on PCB with dimensions 100 mm  $\times$  100 mm  $\times$  1.6 mm

## Recommended Operating Conditions (V<sub>DD</sub> = 4.5 V~5.5 V, $T_{opr}$ = -40°C~85°C unless otherwise specified)

| Characteristics           | Symbol           | Conditions & Pins                                                                   | Min                    | Тур. | Max                    | Unit   |

|---------------------------|------------------|-------------------------------------------------------------------------------------|------------------------|------|------------------------|--------|

| Supply voltage            | $V_{DD}$         | _                                                                                   | 4.5                    | 5.0  | 5.5                    | V      |

| High-level input voltage  | V <sub>IH</sub>  | PI DATA, PI CLK, PI SEL, PI LATCH,<br>SI DATA, SI CLK, SI SEL, SI LATCH,<br>PWM CLK | 0.7<br>V <sub>DD</sub> | _    | V <sub>DD</sub>        | V      |

| Low-level input voltage   | V <sub>IL</sub>  | V <sub>IL</sub> BLANK, LED TEST, TSENA, DOE, DCEN, BCEN                             |                        |      | 0.3<br>V <sub>DD</sub> | V      |

| High-level output current | I <sub>OH</sub>  | PO DATA 00~PO DATA 07, SO DATA                                                      | _                      | _    | -1                     | mA     |

| Low-level output current  | l <sub>OL</sub>  | V <sub>DD</sub> = 4.5 V, ALARM1, ALARM2                                             | _                      |      | 1                      | mA     |

| Constant-current output   | lout             | OUT 00~OUT 15                                                                       | 5                      | -    | 80                     | mA/bit |

| Output voltage            | V <sub>OUT</sub> | OUT 00~OUT 15 OFF                                                                   | _                      |      | 26                     | V      |

| Output voltage            | V <sub>OH</sub>  | ALARM1, ALARM2 OFF                                                                  | _                      | _    | 5                      | V      |

| Operating temperature     | T <sub>opr</sub> | _                                                                                   | -40                    | _    | 85                     | °C     |

8

# Recommended Operating Conditions (continue) ( $V_{DD}=4.5~V\sim5.5~V,~T_{opr}=-40^{\circ}C\sim85^{\circ}C$ unless otherwise specified)

| Characteristics     | Symbol                                 | Condition & Terminals                         | Min | Тур. | Max | Unit     |  |

|---------------------|----------------------------------------|-----------------------------------------------|-----|------|-----|----------|--|

|                     | f <sub>PWM</sub>                       | Ratio of High-level: Low level = 50%, PWM CLK | _   | _    | 10  |          |  |

|                     | f <sub>Pl1</sub>                       | PI CLK,                                       | _   | _    | 15  |          |  |

| Clock frequency     | f <sub>Pl2</sub>                       | PI CLK, connected in cascade                  | _   | _    | 10  | MHz      |  |

|                     | f <sub>SI1</sub>                       | SI CLK                                        | _   | _    | 15  |          |  |

|                     | f <sub>Sl2</sub>                       | SI CLK, connected in cascade                  | _   | _    | 10  |          |  |

|                     | t <sub>wH</sub> /t <sub>wL</sub>       | PWM CLK                                       | 30  | _    | _   |          |  |

|                     | ¹wH/¹wL                                | PI CLK, SI CLK                                | 30  | _    | _   |          |  |

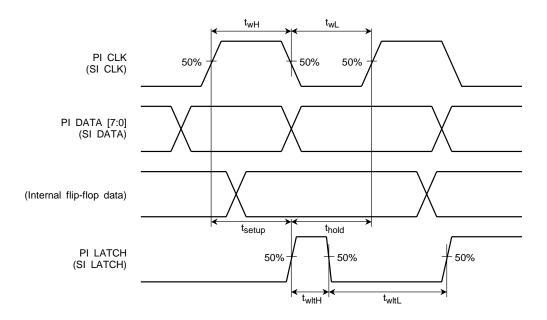

| Minimum pulse width | t <sub>wltH</sub> /t <sub>wltL</sub>   | PI LATCH, SI LATCH                            | 50  | _    | _   | ns       |  |

| Williman paise wath | t <sub>wrstH</sub> /t <sub>wrstL</sub> | RESET                                         | 50  | _    | _   |          |  |

|                     | t <sub>wblkH</sub> /t <sub>wblkL</sub> | BLANK                                         | 400 | _    | _   |          |  |

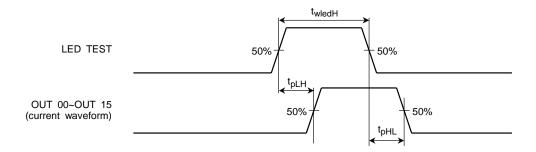

|                     | t <sub>wledH</sub> /t <sub>wledL</sub> | LED TEST                                      | 400 | _    | _   |          |  |

|                     |                                        | PI DATA → PI CLK                              | 10  | _    | _   |          |  |

|                     |                                        | PI LATCH → PI CLK                             | 10  | _    | _   | 1        |  |

| Set-up time         | t <sub>setup</sub>                     | SI DATA → SI CLK                              | 10  | _    | _   | ns       |  |

|                     |                                        | SI LATCH → SI CLK                             | 10  | _    | _   |          |  |

|                     |                                        | SI LATCH → SI CEL                             | 50  | _    | _   |          |  |

|                     |                                        | PI DATA → PI CLK                              | 5   | _    | _   |          |  |

|                     |                                        | PI LATCH → PI CLK                             | 5   | _    | _   | İ        |  |

| Hold time           | t <sub>hold</sub>                      | SI DATA → SI CLK                              | 5   | _    | _   | ns       |  |

|                     |                                        | SI LATCH → SI CLK                             | 5   | _    | _   | <u> </u> |  |

|                     |                                        | SI LATCH → SI CEL                             | 50  | _    | _   |          |  |

9

2006-06-14

## **Electrical Characteristics 1**

$(V_{DD} = 4.5 \text{ V} \sim 5.5 \text{ V}, T_{opr} = -40^{\circ}\text{C} \sim 85^{\circ}\text{C}, \text{ typ: } V_{DD} = 5.0 \text{ V}, T_{opr} = 25^{\circ}\text{C})$

| Parameter                        | Symbol           | Test conditions & Terminals                                                                                       | Min                     | Тур. | Max | Unit |

|----------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----|------|

| High-level output voltage        | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA,<br>PO DATA 00~PO DATA 07, SO DATA                                                      | V <sub>DD</sub><br>-0.4 | _    | _   | V    |

| Low-level output voltage         | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA,<br>PO DATA 00~PO DATA 07, SO DATA                                                       | _                       | _    | 0.4 | ٧    |

|                                  |                  | I <sub>OL</sub> = 1.0 mA, ALARM1, ALARM2                                                                          | _                       | _    | 0.3 |      |

| Tri-state output leakage current | I <sub>OZ</sub>  | V <sub>OUT</sub> = V <sub>DD</sub> or V <sub>SS</sub> ,<br>PO DATA 00~PO DATA 07                                  | _                       | ±0.5 | ±5  | μА   |

| Input current                    | II               | All pins without pull-up/pull-down resistors                                                                      | _                       | _    | ±1  | μΑ   |

|                                  | I <sub>DD1</sub> | PI DATA = 1/2 PI CLK<br>SI DATA = 1/2 SI CLK<br>PI CLK = SI CLK = 20 MHz<br>PWMCLK = L, BLANK = H<br>Settings: *1 |                         | 20   | 30  |      |

|                                  | I <sub>DD2</sub> | PI DATA = SI DATA = L<br>PI CLK = SI CLK = L<br>PWMCLK = 20 MHz<br>Settings: *5a                                  | _                       | 75   | 105 |      |

| Supply current                   | I <sub>DD3</sub> | PI DATA = 1/2 PI CLK<br>SI DATA = 1/2 SI CLK<br>PI CLK = SI CLK = PWMCLK = 20 MHz<br>Settings: *5a                |                         | 80   | 115 | mA   |

|                                  | I <sub>DD4</sub> | PI DATA = SI DATA = L<br>PI CLK = SI CLK = L<br>PWMCLK = 20 MHz<br>Settings: *6a                                  | _                       | 90   | 140 |      |

|                                  | I <sub>DD5</sub> | PI DATA = 1/2 PI CLK<br>SI DATA = 1/2 SI CLK<br>PI CLK = SI CLK = PWMCLK = 20 MHz<br>Settings: *6a                | _                       | 95   | 150 |      |

## **Electrical Characteristic Settings**

## (OUT 00~OUT 15 all on, $V_{OUT}$ = 0.7 V and REXT = 2.7 $k\Omega$ unless otherwise specified)

| No. | DAC Settings                                                          | Surface Brightness<br>Adjustment (DAC3) | Constant Output Current (typ.) |

|-----|-----------------------------------------------------------------------|-----------------------------------------|--------------------------------|

| *1  | Outputs all OFF, V <sub>OUT</sub> = 26 V, DAC1, 2, 4 = MSB, BLANK = H |                                         | I <sub>OUT</sub> = 0 mA        |

| *2  | DAC1 = 0, DAC2 = 0, DAC4 = 63, BLANK = L                              |                                         | I <sub>OUT</sub> = 7.10 mA     |

| *3a | DAC1 = 0, DAC2 = 17, DAC4 = 63, BLANK = L                             |                                         | I <sub>OUT</sub> = 10.0 mA     |

| *4a | DAC1 = 1, DAC2 = 17, DAC4 = 63, BLANK = L                             | DAC3 = 31                               | I <sub>OUT</sub> = 19.9 mA     |

| *5a | DAC1 = 2, DAC2 = 37, DAC4 = 63, BLANK = L                             |                                         | I <sub>OUT</sub> = 40.1 mA     |

| *6a | DAC1 = 3, DAC2 = 51, DAC4 = 63, BLANK = L                             |                                         | I <sub>OUT</sub> = 60.2 mA     |

| *7  | DAC1 = 3, DAC2 = 63, DAC4 = 63, BLANK = L                             |                                         | I <sub>OUT</sub> = 71.0 mA     |

| *3b | DAC1 = 0, DAC2 = 17, DAC4 = 63, BLANK = L                             |                                         | $I_{OUT} = 5.0 \text{ mA}$     |

| *4b | DAC1 = 1, DAC2 = 17, DAC4 = 63, BLANK = L                             | DAC3 = 00                               | I <sub>OUT</sub> = 10.0 mA     |

| *5b | DAC1 = 2, DAC2 = 37, DAC4 = 63, BLANK = L                             | DAC3 - 00                               | I <sub>OUT</sub> = 20.0 mA     |

| *6b | DAC1 = 3, DAC2 = 51, DAC4 = 63, BLANK = L                             |                                         | I <sub>OUT</sub> = 30.1 mA     |

## **Electrical Characteristics 2**

( $V_{DD} = 4.5 \text{ V} \sim 5.5 \text{ V}, T_{opr} = -40 ^{\circ}\text{C} \sim 85 ^{\circ}\text{C}, \text{ typ: } V_{DD} = 5.0 \text{ V}, T_{opr} = 25 ^{\circ}\text{C}$ )

| Parameter                                         | Symbol                           | Test Conditions                                                                             | Min  | Тур.                    | Max  | Unit  |  |

|---------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------|------|-------------------------|------|-------|--|

|                                                   | I <sub>OUT1</sub>                | Settings *7                                                                                 | 60.4 | 71.0                    | 81.6 |       |  |

|                                                   | I <sub>OUT2</sub>                | Settings *6a                                                                                | 51.2 | 60.2                    | 69.2 |       |  |

| Constant current output                           | I <sub>OUT3</sub>                | Settings *5a 34.1                                                                           |      | 40.1                    | 46.1 | V     |  |

| Constant-current output                           | I <sub>OUT4</sub>                | Settings *4a                                                                                | 16.5 | 19.9                    | 23.2 | V     |  |

|                                                   | I <sub>OUT5</sub>                | Settings *3a                                                                                | 7.8  | 10.0                    | 12.2 |       |  |

|                                                   | I <sub>OUT6</sub>                | Settings *2                                                                                 | 4.54 | 7.1                     | 9.65 |       |  |

| Constant-current output Depends on                | %T <sub>OPR1</sub>               | Settings *6a, V <sub>OUT</sub> = 1.0 V, T <sub>opr</sub> is varied in the range –40°C~85°C. | _    | ±50                     | ±80  | иА/°С |  |

| temperature                                       | %T <sub>OPR2</sub>               | Settings *4a, V <sub>OUT</sub> = 1.0 V, T <sub>opr</sub> is varied in the range _40°C~85°C. | _    | ±25                     | ±50  | μΑ/Ο  |  |

| Leakage current for constant-current output       | I <sub>OLK</sub>                 | Settings *1, V <sub>OUT</sub> = 26 V                                                        | _    | 0.05                    | 0.1  | μА    |  |

|                                                   | Δl <sub>OUT1</sub>               | Settings *6a, V <sub>OUT</sub> = 0.7 V                                                      | _    | ±2.5                    | ±6   |       |  |

| Constant current accuracy between                 | Δl <sub>OUT2</sub>               | Settings *5a, V <sub>OUT</sub> = 0.7 V                                                      | _    | ±3.5                    | ±6   | %     |  |

| bits                                              | ∆l <sub>OUT3</sub>               | Settings *4a, V <sub>OUT</sub> = 0.7 V                                                      | _    | ±5.5                    | ±7   | /0    |  |

|                                                   | ∆l <sub>OUT4</sub>               | Settings *3a, V <sub>OUT</sub> = 0.7 V                                                      | _    | ±7                      | ±12  |       |  |

|                                                   | %l <sub>OUT1</sub>               | Settings is changed from *6a to *6b.                                                        | _    | ±1                      | ±3   |       |  |

| Dot adjustment deviation between bits             | %l <sub>OUT2</sub>               | Settings is changed from *5a to *5b.                                                        | _    | ±1.5                    | ±3   | %     |  |

| (when DAC3 data were changed from MSB to LSB.)    | %I <sub>OUT3</sub>               | Settings is changed from *4a to *4b.                                                        | _    | ±3.5                    | ±5   | /6    |  |

| ,                                                 | %l <sub>OUT4</sub>               | Settings is changed from *3a to *3b.                                                        | _    | ±6                      | ±12  |       |  |

| Constant-current output depends on                | %V <sub>OUT</sub>                | Settings *6a, V <sub>OUT</sub> is varied in the range 0.7 V~3 V.                            | _    | ±5                      | ±8   | %     |  |

| output voltage                                    | 70 V OU I                        | Settings *4a, V <sub>OUT</sub> is varied in the range 0.7 V~3 V.                            | _    | ±3                      | ±6   | 70    |  |

| Constant-current output depends on supply voltage | %V <sub>DD</sub>                 | Settings *6a, V <sub>DD</sub> is varied in the range 4.5 V~5.5 V.                           | _    | ±1                      | ±2   | %     |  |

| TCD detection temperature                         | T <sub>sd1</sub>                 | _                                                                                           | 120  | 140                     | 160  | °C    |  |

| TSD detection temperature                         | T <sub>sd2</sub>                 | _                                                                                           | 140  | 160                     | 180  |       |  |

| Output-open detection voltage                     | V <sub>ARL</sub>                 | ALARM2                                                                                      | _    | 0.04<br>V <sub>DD</sub> | _    | V     |  |

| Pull-up/down resistor                             | R <sub>up</sub> /R <sub>dw</sub> | _                                                                                           | 150  | 300                     | 600  | kΩ    |  |

## **Electrical Characteristic Settings**

## (OUT 00~OUT 15 all on, $V_{OUT}$ = 0.7 V and REXT = 2.7 $k\Omega$ unless otherwise specified)

| No. | DAC Settings                                                   | All Dot Adjustment (DAC3) | Constant Output Current (typ.) |

|-----|----------------------------------------------------------------|---------------------------|--------------------------------|

| *1  | OUT00~15 OFF, V <sub>OUT</sub> = 26 V, DAC1~4 = MSB, BLANK = H |                           | I <sub>OUT</sub> = 0 mA        |

| *2  | DAC1 = 0, DAC2 = 0, DAC4 = 63, BLANK = L                       |                           | I <sub>OUT</sub> = 7.10 mA     |

| *3a | DAC1 = 0, DAC2 = 17, DAC4 = 63, BLANK = L                      |                           | $I_{OUT} = 10.0 \text{ mA}$    |

| *4a | DAC1 = 1, DAC2 = 17, DAC4 = 63, BLANK = L                      | DAC3 = 31                 | $I_{OUT} = 19.9 \text{ mA}$    |

| *5a | DAC1 = 2, DAC2 = 37, DAC4 = 63, BLANK = L                      |                           | $I_{OUT} = 40.1 \text{ mA}$    |

| *6a | DAC1 = 3, DAC2 = 51, DAC4 = 63, BLANK = L                      |                           | $I_{OUT} = 60.2 \text{ mA}$    |

| *7  | DAC1 = 3, DAC2 = 63, DAC4 = 63, BLANK = L                      |                           | $I_{OUT} = 71.0 \text{ mA}$    |

| *3b | DAC1 = 0, DAC2 = 17, DAC4 = 63, BLANK = L                      |                           | $I_{OUT} = 5.0 \text{ mA}$     |

| *4b | DAC1 = 1, DAC2 = 17, DAC4 = 63, BLANK = L                      | DAC3 = 00                 | $I_{OUT} = 10.0 \text{ mA}$    |

| *5b | DAC1 = 2, DAC2 = 37, DAC4 = 63, BLANK = L                      | DA03 = 00                 | $I_{OUT} = 20.0 \text{ mA}$    |

| *6b | DAC1 = 3, DAC2 = 51, DAC4 = 63, BLANK = L                      |                           | I <sub>OUT</sub> = 30.1 mA     |

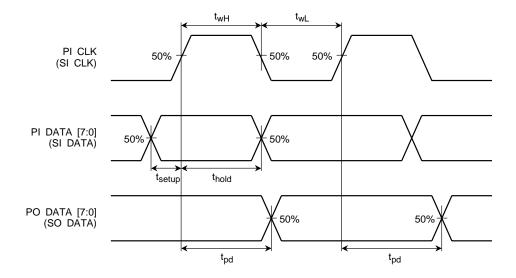

Switching Characteristics (V<sub>DD</sub> = 4.5 V~5.5 V, T<sub>opr</sub> =  $-40^{\circ}$ C~85°C, C<sub>L</sub> = 50 pF unless otherwise specified, typ: V<sub>DD</sub> = 5.0 V, T<sub>opr</sub> = 25°C, C<sub>L</sub> = 50 pF)

| Parameter                                  | Symbol               | Test Conditions                    | Min | Тур. | Max | Unit |  |

|--------------------------------------------|----------------------|------------------------------------|-----|------|-----|------|--|

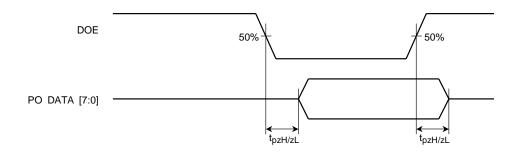

| Tri-state output enable propagation delay  | t <sub>pZH</sub> /zL | DOE → PO DATA0~ PO DATA 7          | 8   | 16   | 30  | ns   |  |

| Tri-state output disable propagation delay | t <sub>pHZ</sub> /LZ | DOE → PO DATA0~ PO DATA 7          | 8   | 16   | 30  | ns   |  |

| Rise time                                  | +                    | OUT00~ OUT 15                      | 10  | 17   | 30  | μS   |  |

| Nise time                                  | t <sub>r</sub>       | ALARM1, ALARM2                     | 0.2 | 0.4  | 0.8 | ns   |  |

| Fall time                                  | 4.                   | OUT00~ OUT 15                      | 20  | 40   | 70  | ns   |  |

| ran ume                                    | t <sub>f</sub>       | ALARM1, ALARM2                     | 2   | 4    | 8   | 115  |  |

|                                            | t <sub>pHL</sub>     | BLANK → OUT00~ OUT 15              | 30  | 60   | 120 |      |  |

|                                            | t <sub>pLH</sub>     | PWM CLK → OUT00~ OUT 15            | 70  | 120  | 200 |      |  |

|                                            | t <sub>pHL</sub>     | PWM CLK → OUT00~ OUT 15            | 40  | 70   | 140 |      |  |

|                                            | t <sub>pLH</sub>     | LED TEST → OUT00~ OUT 15           | 60  | 110  | 190 |      |  |

| Drangation dolor                           | t <sub>pHL</sub>     | 1 LED 1ES1 → 00100~ 001 15         | 30  | 60   | 130 |      |  |

| Propagation delay                          | t <sub>pHL</sub>     | RESET → OUT00~ OUT 15              | 30  | 60   | 130 | ns   |  |

|                                            |                      | PI CLK → PO DATA0~ PO DATA 7       | 20  | 30   | 70  |      |  |

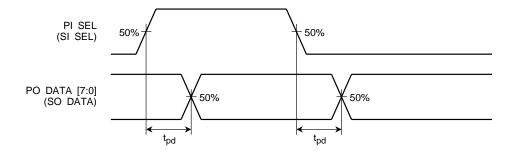

|                                            |                      | PI SEL → PO DATA0~ PO DATA 7 20 30 |     | 30   | 70  |      |  |

|                                            | t <sub>pd</sub>      | SI SEL → SO DATA                   | 10  | 18   | 40  |      |  |

|                                            |                      | SI SEL → SO DATA                   | 10  | 20   | 40  |      |  |

## **Explanation of Operation and Truth Tables**

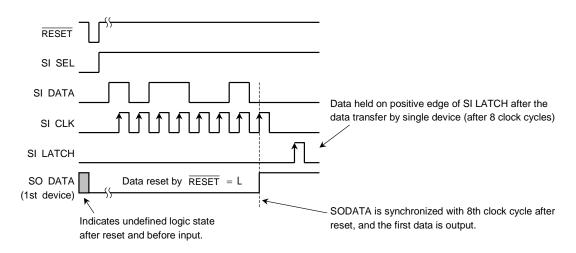

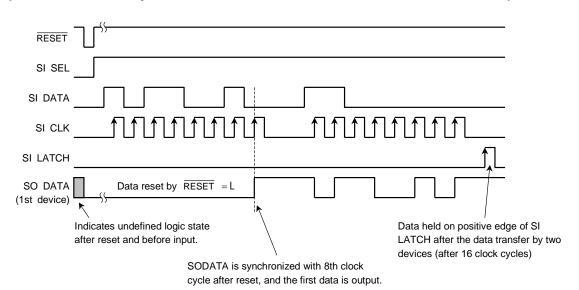

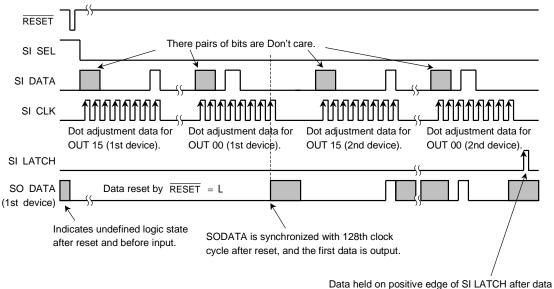

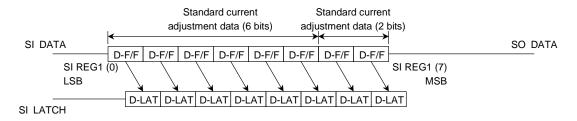

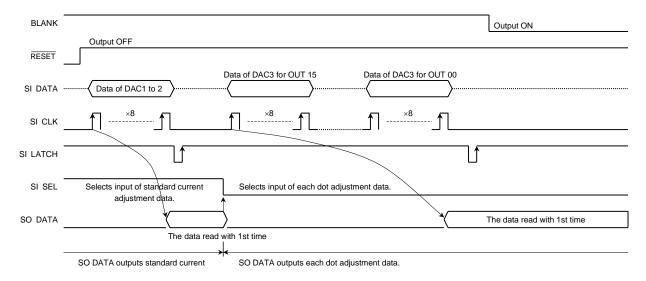

## Serial data transfer: standard current adjustment using DAC1 and DAC2 (data register SI REG [7:0])

| Process | SI DATA | SI CLK | SI LATCH | SI SEL | SO DATA      | Operation and Function                                                                                                                                                      |

|---------|---------|--------|----------|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ₩ or l  | (×8)   | L        | Н      | H or L       | Selects standard current adjustment (8 bits, 2 bits and 6 bits) for input data when SI SEL is high. Data is transferred to SI REG [1] on 8th positive edge of SI CLK input. |

| 2       | H or L  |        | (×1)     | н      | No<br>change | Holds the data transferred to SI REG [1] on positive edge of SI LATCH. Set is reflected on standard current adjustment from the moment when it is held.                     |

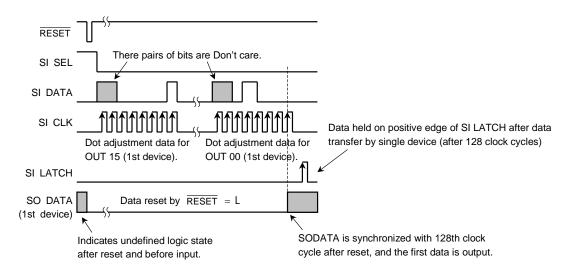

## Serial data transfer timing (standard current adjustment, SI SEL = H, single device)

## Serial data transfer timing (standard current adjustment, SI SEL = H, two devices connected in cascade)

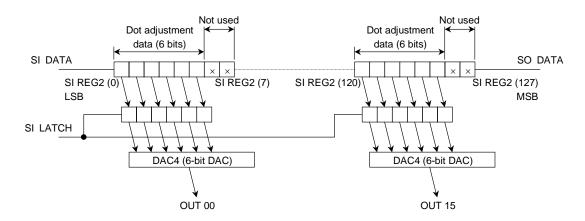

## Serial data transfer: dot adjustment DAC4. (data register SI REG2 [127:0])

| Process | SI DATA | SI CLK | SI LATCH | SI SEL | SO DATA      | Operation and Function                                                                                                                 |

|---------|---------|--------|----------|--------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1       | H or L  | (×128) | L        | L      | H or L       | Selects dot adjustment (128 bits) for input data. Data is transferred to SI REG2 on 128th positive edge of SI CLK.                     |

| 2       | 11011   | L      | (×1)     | L      | No<br>change | Holds the data transferred to SI REG2 on positive edge of SILATCH. Set is reflected on dot adjustment from the moment when it is held. |

## Serial data transfer timing (dot adjustment, SI SEL = L, single device)

## Serial data transfer timing (dot adjustment, SI SEL = L, two devices connected in cascade)

transfer by two devices (after 256 clock cycles)

## DAC1: Standard current adjustment settings for DAC1 (SI REG1 [7:6])

| RESET | SI SEL | SI REG<br>(7:6) | SI REG<br>(5:0) | Current<br>Rate | Operation and Function                                                                                                                | Notes                                             |

|-------|--------|-----------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Н     | Н      | НН              | xxxxxx          | 100%<br>(1.0)   | 100% of base current setting as determined by $R_{\text{EXT}}$ $(\Omega)$                                                             | When SI SEL =                                     |

| Н     | Н      | HL              | xxxxxx          | 75%<br>(0.75)   | 75% of base current setting as determined by $R_{\text{EXT}}$ $(\Omega)$                                                              | H, 2 bits on<br>MSB sides are<br>corresponding to |

| Н     | Н      | LH              | xxxxxx          | 50%<br>(0.5)    | 50% of base current setting as determined by $R_{\text{EXT}}$ $(\Omega)$                                                              | set of standard<br>current<br>adjustment          |

| Н     | Н      | LL              | xxxxxx          | 25%<br>(0.25)   | 25% of base current setting as determined by $R_{\text{EXT}}$ $(\Omega)$                                                              | DÁC1.<br>The output<br>current can be             |

|       | Х      | LL              | LLLLLL          | 25%<br>(0.25)   | Initial state after input of reset signal: 25% of base current setting as determined by $R_{\text{EXT}}(\Omega)$ (as described above) | set to one of 4 levels.                           |

## DAC2: Standard current adjustment settings for DAC2 (SI REG1 [5:0])

| RESET | SI SEL | SI REG<br>(7:6) | SI REG<br>(5:0)            | Current<br>Rate                                  | Operation and Function                                                                                                                                                                                    | Notes                                                                                                         |

|-------|--------|-----------------|----------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Н     | Н      | XX              | xxxxxx                     | 100%<br>(1.0)                                    | 100% of base current value as set using DAC1 base current adjustment                                                                                                                                      |                                                                                                               |

| н     | н      | xx              | HHHHHL<br>↑<br>↓<br>LLLLLH | (0.9905)  ↑  1LSB = ±0.95% (±0.0095)  ↓ (0.4095) | Any one or 64 levels in the range 40%~100% of the current can be set. (1 LSB = 0.95%) 6-bit DAC performance 1LSB variation: ±0.95% Non linearity error: ±1/2LSB Differential non linearity error: ±3/4LSB | When SI SEL = H, 6 bits on MSB sides are corresponding to set of standard current adjustment DAC2. The output |

| Н     | н      | XX              | LLLLLL                     | 40%<br>(0.4)                                     | 40% of base current value as set using DAC1 base current adjustment                                                                                                                                       | set to one of 64 levels.                                                                                      |

|       | Х      | LL              | LLLLLL                     | 40%<br>(0.4)                                     | Initial state after input of reset signal: 40% of base current value set as described above                                                                                                               |                                                                                                               |

## DAC4: Set details of dot adjustment DAC4 (SI REG2 [127:0])

| RESET | SI SEL | DCEN | About 8 bits<br>Unit of SI<br>REG2 [127:0] | Current<br>Rate                                                   | Operation and Function                                                                                                                                                                                    | Notes                                                                                                                                                |

|-------|--------|------|--------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н     | L      | Ħ    | ХХННННН                                    | 100%<br>(1.0)                                                     | Output current is 100% of base current value as set using DAC1 and DAC2 base current adjustment and DAC3 surface brightness adjustment                                                                    | When SI SEL = L<br>8 bits out of 128 bits are<br>corresponding to set of<br>each output, and the 6 bits<br>on MSB sides of 8 bits are                |

| н     | L      | н    | XXHHHHHL                                   | (0.9874)<br>↑<br>1LSB =<br>±1.269%<br>(±0.0126)<br>↓<br>(20.0126) | Any one of 64 levels in the range 20%-100% of the current can be set. (1LSB ≈ 1.27%) 6-bit DAC performance 1LSB variation: ±1.269% Non linearity error: ±1/2LSB Differential non linearity error: ±1/2LSB | on MSB sides of 8 bits are data on dot adjustment.  The output current can be set to one of 64 levels.  SI REG2 [7:0]  → adjustment data for OUT 00. |

| Н     | L      | Н    | XXLLLLL                                    | 20%<br>(0.2)                                                      | 20% of base current value as set using DAC3 surface brightness adjustment                                                                                                                                 | SI REG2 [15:8]  → adjustment data for OUT 01.                                                                                                        |

|       | X      | Η    | XXLLLLLL                                   | 20%<br>(0.2)                                                      | Initial state after input of reset signal: 20% of base current value set as described above                                                                                                               | SI REG2 [127:120]<br>→ adjustment data for<br>OUT 15.                                                                                                |

| Н     | Х      | L    | ХХННННН                                    | 100%<br>(1.0)                                                     | Output current is 100% of base current value set as described above.                                                                                                                                      | Data input is still enabled if DCEN = L. If DCEN = H, adjustment is performed at the same time.                                                      |

15

Polarity of serial input data for standard current adjustment (SI REG1 [7:0]) and dot adjustment (SI REG2 [127:0])

### Serial data transfer timing

(SI SEL = H, input of standard current adjustment data for DAC1 and DAC2)

## Serial data transfer timing (SI SEL = L, input of dot adjustment data for DAC4)

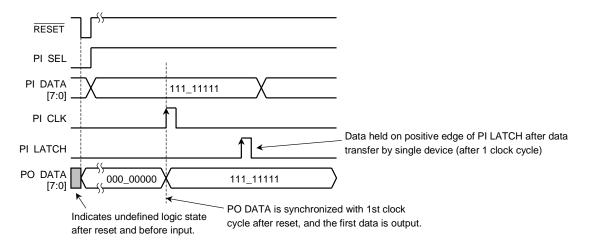

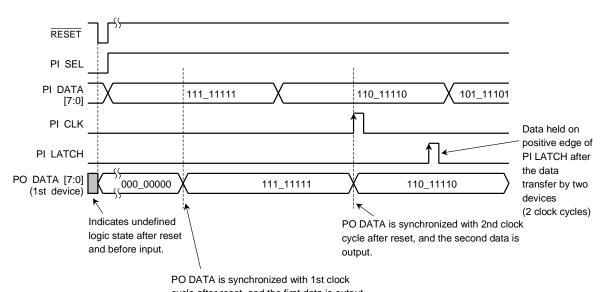

## Parallel data transfer: All dot adjustment DAC3. (data register PI REG1 [7:0])

| Process | PI DATA<br>[7:0] | PI CLK | PI LATCH | PI SEL | PO DATA<br>[7:0] | Operation and Function                                                                                                                 |

|---------|------------------|--------|----------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1       | H or L           | (×1)   | L        | н      | H or L           | Selects total dot adjustment (8-bit, 3-bit and 5-bit) for input data. Data is transferred to PI REG1 on 128th positive edge of PI CLK. |

| 2       | HOIL             | L      | (×1)     | Н      | No<br>change     | Holds the data transferred to PI REG1. Set is reflected on all dot adjustment from the moment when it is held.                         |

### Parallel data transfer timing (all dot adjustment, PI SEL = H, single device)

## Parallel data transfer timing (all dot adjustment, PI SEL = H, two devices connected in cascade)

cycle after reset, and the first data is output.

17

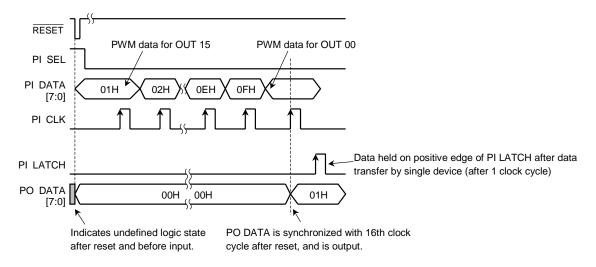

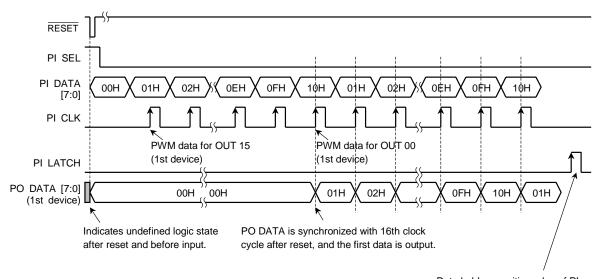

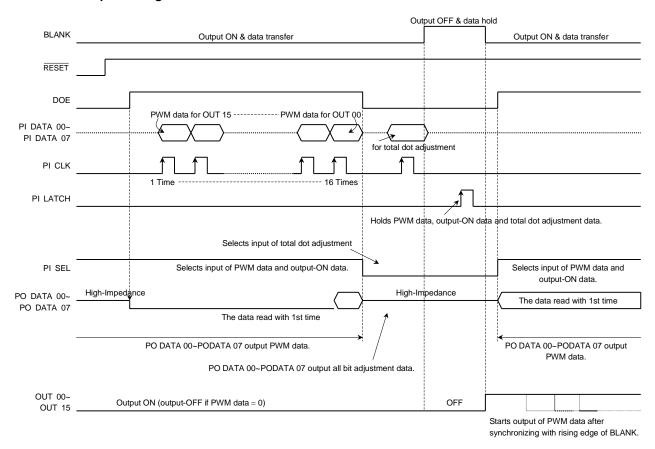

## Parallel data transfer PMW display data (data register PI REG2 [127:0])

| Process | PI DATA | PI CLK | PI LATCH | PI SEL | PO DATA      | Operation and Function                                                                                                   |

|---------|---------|--------|----------|--------|--------------|--------------------------------------------------------------------------------------------------------------------------|

| 1       | H or L  | (×16)  | L        | L      | H or L       | Selects for input data of PWM display data (8 bit × 16). Data is transferred to PI REG2 on 16th positive edge of PI CLK. |

| 2       | HOIL    | L      | (×1)     | L      | No<br>change | Holds the data transferred to PI REG2. Set is reflected on PWM 256 grayscales from the next BLANK = L when it is held.   |

## Parallel data transfer timing (PWM data PI SEL = L, single device)

### Parallel data transfer timing (PWM data PI SEL = L, two devices connected in cascade)

Data held on positive edge of PI LATCH after data transfer by two devices (32 clock cycles)

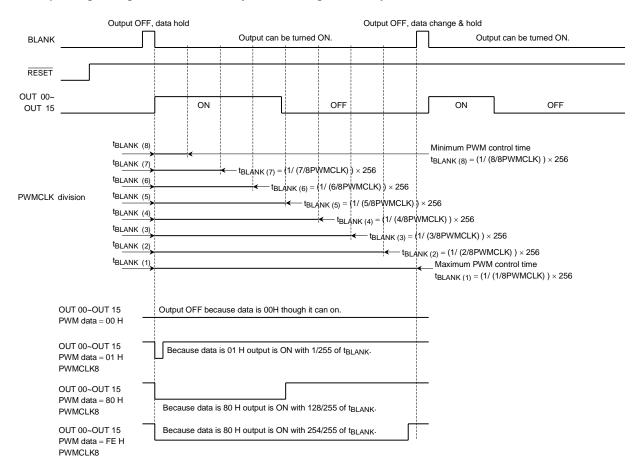

## Details all dot adjustment setting using PWMCLK division (PI REG1 [7:5])

| RESET | PI SEL | BCEN | PI REG1<br>[7:5] | PWMCLK<br>Divisor               | Operation and Function                                                                                                                                  | Notes                                                                                                                                                 |

|-------|--------|------|------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н     | I      | Н    | LLL              | PWM CLK =<br>8/8 PWMCLK<br>(Hz) | The period of PWMCLK is set to equal the change in the PWM pulse width data. 1LSB.                                                                      | When PI SEL = H is selected, 3                                                                                                                        |

| н     | н      | н    | LLH<br>←<br>HHL  | 7/8 PWMCLK<br>to<br>2/8 PWMCLK  | Variable does the frequency of<br>PWMCLK to 1/8 of the minimal. It<br>is set in 8 levels.<br>6-bit DAC performance<br>Maximum input: PWMCLK = 20<br>MHz | bits on MSB sides are corresponding to set of standard current adjustment by PWM frequency dividing.  PI REG [7:5] varies the pulse width of PWM data |

| Н     | н      | Н    | ННН              | PWMCLK =<br>1/8 PWMCLK<br>(Hz)  | The period of PWMCLK is set to one-eighth the change in the PWM pulse width data. 1 LSB.                                                                | corresponding to 1 LSB for eight levels and adjusts brightness. This setting values affects pulse widths on all outputs.                              |

|       | Х      | Н    | LLL              | PWMCLK =<br>8/8 PWMCLK<br>(Hz)  | The period of PWMCLK is set to equal the change in the PWM pulse width data. 1 LSB.                                                                     | widths on an outputs.                                                                                                                                 |

| Н     | Н      | L    | XXX              | Unchanged                       | BCEN signal does not affect PWMCLK frequency dividing.                                                                                                  | Data input is still enabled if BCEN = L. Output current level reflects input settings.                                                                |

## DAC3: Details of all dot adjustment setting for DAC3 (PI REG2 [4:0])

| RESET | PI SEL | PI REG1<br>[4:0]               | BCEN | Current<br>Rate                                           | Operation and Function                                                                                                                                                                                                                    | Notes                                                                                                                                                                        |

|-------|--------|--------------------------------|------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н     | н      | ннннн                          | I    | 100%<br>(1.0)                                             | 100% of base current value as<br>set using DAC1 and DAC2<br>current adjustment and DAC4 dot<br>adjustment                                                                                                                                 |                                                                                                                                                                              |

| н     | н      | HHHHL<br>↑<br>——<br>↓<br>LLLLH | н    | (0.9839)<br>↑  1LSB =<br>±1.61%<br>(±0.0161)  ↓  (0.5161) | Any one of 32 levels in the range 50%~100% of the current can be set. (1 LSB = 1.61%) 5-bit DAC performance 1LSB variation: ±1.61% Non linearity error: ±1/2LSB Differential non linearity error: ±1/2LSB (No guarantee for monotonicity) | When PI SEL = H is selected,<br>5 bits on LSB side are<br>corresponding to set of surface<br>brightness adjustment.<br>The output current can be set<br>to one of 32 levels. |

| н     | н      | LLLLL                          | I    | 50%<br>(0.5)                                              | 50% of base current value as set using DAC1 and DAC2 current adjustment and DAC4 dot adjustment                                                                                                                                           |                                                                                                                                                                              |

|       | X      | ННННН                          | Н    | 100%<br>(1.0)                                             | Initial state after input of reset signal: 100% of base current value set as described above                                                                                                                                              |                                                                                                                                                                              |

| н     | Х      | ННННН                          | L    | 100%<br>(1.0)                                             | Initial state after input of DCEN signal: 100% of base current value set as described above                                                                                                                                               | Data input is still enabled if<br>BCEN = L.<br>If BCEN = H, adjustment is<br>performed at the same time.                                                                     |

### Detailed PWM 256 grayscales setting (PI REG2 [127:0], 16 × 8 bits)

| RESET | PI SEL | 1 word (8 bits)<br>of PI REG2 | Output Pulse<br>Rate | Operation and Function                                                                       | Notes                                                                                                                                                                   |

|-------|--------|-------------------------------|----------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н     | L      | ннннннн                       | 255/255<br>100%      | Output pulse width is at its maximum value when input data is FF.                            | When PI SEL = L, The PWM grayscale controls the output pulse width.                                                                                                     |

| н     | L      | HHHHHHHL                      | _                    | The input data can be used to control the PWM pulse width and hence generate 256 grayscales. | 16 × 8-bit words are transferred in parallel. 1 word is the PWM data of each output pulse width is set in 256 step. PI REG2 [7:0] → PWM data for OUT 00. PI REG2 [15:8] |

| Н     | L      | LLLLLLLL                      | 0/255<br>0%          | Outputs are OFF when the input data is 00.                                                   | → PWM data for OUT 01. PI REG2 [127:120] → PWM data for OUT 15.                                                                                                         |

|       | X      | LLLLLLLL                      | 0/255<br>0%          | Early condition after the reset signal input is set in 0/256 (output off).                   | Minimum output pulse width is 1/PWMCLK.                                                                                                                                 |

Polarity of serial input data for all dot adjustment (PI REG [7:0]) and PWM 256 grayscales (PI REG2 [127:0])

## Parallel data transfer timing

(PI SEL = H, selects data input for all dot adjustment for DAC3.)

(PI SEL = L, selects data input for PWM 256 grayscales.)

### Reference table: output current setting vales (1)

|     | DAC1 (2-bit) |                  |          | DAC2 (6-bit)     |                  |     | DAC3 (5-bit)   |                  |          | DAC4 (6-bit)     |                 |

|-----|--------------|------------------|----------|------------------|------------------|-----|----------------|------------------|----------|------------------|-----------------|

| No. | Input Data   | Current<br>Rate1 | No.      | Input Data       | Current<br>Rate2 | No. | Input Data     | Current<br>Rate3 | No.      | Input Data       | Currer<br>Rate4 |

| 3   | 11           | 1.00             | 63       | 111111           | 1.000            | 31  | **11111        | **1.000          | 63       | 111111           | 63              |

| 2   | 10           | 0.75             | 62       | 111110           | 0.990            | 30  | 11110          | 0.984            | 62       | 111110           | 62              |

| 1   | 01           | 0.50             | 61       | 111101           | 0.981            | 29  | 11101          | 0.968            | 61       | 111101           | 61              |

| 0   | **00         | **0.25           | 60       | 111100           | 0.971            | 28  | 11100          | 0.952            | 60       | 111100           | 60              |

| _   | _            | _                | 59       | 111011           | 0.962            | 27  | 11011          | 0.936            | 59       | 111011           | 59              |

| _   | _            | _                | 58       | 111010           | 0.952            | 26  | 11010          | 0.919            | 58       | 111010           | 58              |

| _   | _            |                  | 57       | 111001           | 0.943            | 25  | 11001          | 0.903            | 57       | 111001           | 57              |

| _   | _            | -                | 56       | 111000           | 0.933            | 24  | 11000          | 0.887            | 56       | 111000           | 56              |

| _   | _            | 1                | 55       | 110111           | 0.924            | 23  | 10111          | 0.871            | 55       | 110111           | 55              |

| _   | _            |                  | 54       | 110110           | 0.914            | 22  | 10110          | 0.855            | 54       | 110110           | 54              |

| _   | _            | _                | 53       | 110101           | 0.905            | 21  | 10101          | 0.839            | 53       | 110101           | 53              |

| _   | _            | _                | 52       | 110100           | 0.895            | 20  | 10100          | 0.823            | 52       | 110100           | 52              |

| _   | _            | I                | 51       | 110011           | 0.886            | 19  | 10011          | 0.807            | 51       | 110011           | 51              |

| _   | _            | 1                | 50       | 110010           | 0.876            | 18  | 10010          | 0.790            | 50       | 110010           | 50              |

| _   | _            | 1                | 49       | 110001           | 0.867            | 17  | 10001          | 0.774            | 49       | 110001           | 49              |

| _   | _            | I                | 48       | 110000           | 0.857            | 16  | 10000          | 0.758            | 48       | 110000           | 48              |

| _   | _            |                  | 47       | 101111           | 0.848            | 15  | 01111          | 0.742            | 47       | 101111           | 47              |

| _   | _            | I                | 46       | 101110           | 0.838            | 14  | 01110          | 0.726            | 46       | 101110           | 46              |

| _   | _            | I                | 45       | 101101           | 0.829            | 13  | 01101          | 0.710            | 45       | 101101           | 45              |

| _   |              | I                | 44       | 101100           | 0.819            | 12  | 01100          | 0.694            | 44       | 101100           | 44              |

| _   | _            |                  | 43       | 101011           | 0.820            | 11  | 01011          | 0.677            | 43       | 101011           | 43              |

| _   |              |                  | 42       | 101010           | 0.800            | 10  | 01010          | 0.661            | 42       | 101010           | 42              |

| _   | _            |                  | 41       | 101001           | 0.791            | 9   | 01001          | 0.645            | 41       | 101001           | 41              |

| _   | _            | _                | 40       | 101000           | 0.781            | 8   | 01000          | 0.629            | 40       | 101000           | 40              |

| _   | _            | _                | 39       | 100111           | 0.771            | 7   | 00111          | 0.613            | 39       | 100111           | 39              |

|     | _            | _                | 38       | 100110           | 0.762            | 6   | 00110          | 0.597            | 38       | 100110           | 38              |

|     | _            | _                | 37       | 100101           | 0.752            | 5   | 00101          | 0.581            | 37       | 100101           | 37              |

|     | _            | -                | 36       | 100100           | 0.743            | 4   | 00100          | 0.565            | 36       | 100100           | 36              |

|     | _            | -                | 35       | 100011           | 0.733            | 3   | 00011          | 0.549            | 35       | 100011           | 35              |

|     | _            | -                | 34       | 100010           | 0.724            | 2   | 00010          | 0.532            | 34       | 100010           | 34              |

| _   |              |                  | 33       | 100001           | 0.714            | 1   | 00001          | 0.516            | 33       | 100001           | 33              |

|     |              |                  | 32       | 100000           | 0.705            | 0   | 00000          | 0.500            | 32       | 100000           | 32              |

| _   | _            | l                | 31       | 011111           | 0.695            | _   | _              | _                | 31       | 011111           | 31              |

| _   | _            | l                | 30       | 011110           | 0.686            | _   | _              | _                | 30       | 011110           | 30              |

|     | _            | _                | 29       | 011101           | 0.676            | _   | _              | _                | 29       | 011101           | 29              |

|     | _            |                  | 28       | 011100           | 0.667            | _   | _              |                  | 28       | 011100           | 28              |

|     | _            |                  | 27       | 011011           | 0.657            |     | _              |                  | 27       | 011011           | 27              |

| _   | _            |                  | 26       | 011010           | 0.648            | _   | _              |                  | 26       | 011010           | 26              |

|     |              |                  | 25       | 011001           | 0.638            |     |                |                  | 25       | 011001           | 25              |

|     | _            | _                | 24       | 011000           | 0.629            | _   | _              |                  | 24       | 011000           | 24              |

|     | _            |                  | 23       | 010111           | 0.619            | _   | _              | _                | 23<br>22 | 010111           | 23<br>22        |

|     |              |                  | 22<br>21 | 010110<br>010101 | 0.610<br>0.600   |     | _              |                  | 22       | 010110<br>010101 | 22              |

|     | _            |                  | 20       | 010101           | 0.600            | _   | _              |                  | 20       | 010101           | 20              |

|     |              |                  | 19       | 010100           | 0.591            | _   | _              |                  | 19       | 010100           | 19              |

|     | _            |                  | 18       | 010011           | 0.571            |     | _              |                  | 18       | 010011           | 18              |

|     | _            |                  | 17       | 010010           | 0.562            | _   | _              |                  | 17       | 010010           | 17              |

| _   |              |                  | 16       | 010001           | 0.552            |     |                |                  | 16       | 010001           | 16              |

|     |              |                  | 15       | 001111           | 0.532            |     |                |                  | 15       | 001111           | 15              |

| _   | <u> </u>     |                  | 14       | 001111           | 0.533            |     | _              |                  | 14       | 001111           | 14              |

| _   | _            |                  | 13       | 001101           | 0.524            | _   | _              |                  | 13       | 001101           | 13              |

|     |              |                  | 12       | 001101           | 0.524            |     |                |                  | 12       | 001101           | 12              |

|     |              |                  | 11       | 001001           | 0.505            |     |                |                  | 11       | 001100           | 11              |

| _   | _            |                  | 10       | 001010           | 0.495            | _   | _              | _                | 10       | 001011           | 10              |

| _   | _            |                  | 9        | 001001           | 0.486            | _   | _              |                  | 9        | 001001           | 9               |

| _   | _            |                  | 8        | 001000           | 0.476            | _   | _              |                  | 8        | 001001           | 8               |

| _   | _            |                  | 7        | 000111           | 0.467            | _   | _              |                  | 7        | 000111           | 7               |

|     |              |                  | 6        | 000111           | 0.457            |     |                |                  | 6        | 000111           | 6               |

|     | _            |                  | 5        | 000110           | 0.448            |     | _              |                  | 5        | 000110           | 5               |

|     | _            |                  | 4        | 000101           | 0.448            |     | _              |                  | 4        | 000101           | 4               |

|     |              |                  | 3        | 000100           | 0.436            |     | <u> </u>       |                  | 3        | 000100           | 3               |

|     | _            |                  | 2        | 000011           | 0.429            | _   | _              |                  | 2        | 000011           | 2               |

|     | _            |                  | 1        | 000010           | 0.419            |     | <del>-</del> - |                  | 1        | 000010           | 1               |

| _   | . —          | _                | . '      | 000001           | 0.410            | ı — | _              | _                | i '      | 00000 I          | '               |

Note 7: \*\*: Indicates post-reset initialization value ( $\overline{\text{RESET}} = L$ ).

Note 8: The formula for calculating resistance settings is as follows: This value is theory value. Actual current value contains error and so on in this value. REXT  $[k\Omega] = (1.9 \times \text{current rate } 1 \times \text{current rate } 2 \times \text{current rate } 3 / \text{output current } [mA]) \times (1 + (7 \times \text{current rate } 4 / 105)) \times 19.4$  Reference table: output current setting value (2) Reference value for standard current adjustment under conditions:  $R_{EXT} = 2.7 \text{ k}\Omega$  (fixed), all dot adjustment = MSB and dot adjustment = MSB

Unit: mA DAC2 0 2 3 4 5 6 7 8 12 15 1 9 10 11 13 14 7.1 7.3 7.4 7.6 7.8 7.9 8.1 8.3 8.5 8.6 8.8 9.0 9.1 9.3 9.5 9.6 14.2 14.5 14.9 15.2 15.6 15.9 16.2 16.6 16.9 17.2 17.6 17.9 18.3 18.6 18.9 19.3 DAC1 21.3 21.8 22.3 22.8 23.3 23.8 24.3 24.9 25.4 25.9 26.4 26.9 27.4 27.9 28.4 28.9 2 3 28.4 29.1 29.6 30.4 31.1 31.8 32.5 33.1 33.8 34.5 35.2 35.8 36.5 37.2 37.9 38.6

|      |   |      |      |      |      |      |      |      | DA   | .C2  |      |      |      |      |      |      |      |

|------|---|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

|      |   | 16   | 17   | 18   | 19   | 20   | 21   | 22   | 23   | 24   | 25   | 26   | 27   | 28   | 29   | 30   | 31   |

|      | 0 | 9.8  | 10.0 | 10.1 | 10.3 | 10.5 | 10.7 | 10.8 | 11.0 | 11.2 | 11.3 | 11.5 | 11.7 | 11.8 | 12.0 | 12.2 | 12.3 |

| 2    | 1 | 19.6 | 19.9 | 20.3 | 20.6 | 21.0 | 21.3 | 21.6 | 22.0 | 22.3 | 22.7 | 23.0 | 23.3 | 23.7 | 24.0 | 24.3 | 24.7 |

| DAC1 | 2 | 29.4 | 29.9 | 30.4 | 30.9 | 31.4 | 32.0 | 32.5 | 33.0 | 33.5 | 34.0 | 34.5 | 35.0 | 35.5 | 36.0 | 36.5 | 37.0 |

|      | 3 | 39.2 | 39.9 | 40.6 | 41.2 | 41.9 | 42.6 | 43.3 | 44.0 | 44.6 | 45.3 | 46.0 | 46.7 | 47.3 | 48.0 | 48.7 | 49.4 |

|      |   |      |      |      |      |      |      |      | DA   | .C2  |      |      |      |      |      |      |      |

|------|---|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

|      |   | 32   | 33   | 34   | 35   | 36   | 37   | 38   | 39   | 40   | 41   | 42   | 43   | 44   | 45   | 46   | 47   |

|      | 0 | 12.5 | 12.7 | 12.9 | 13.0 | 13.2 | 13.4 | 13.5 | 13.7 | 13.9 | 14.0 | 14.2 | 14.4 | 14.5 | 14.7 | 14.9 | 15.0 |

| 2    | 1 | 25.0 | 25.4 | 25.7 | 26.0 | 26.4 | 26.7 | 27.0 | 27.4 | 27.7 | 28.1 | 28.4 | 28.7 | 29.1 | 29.4 | 29.8 | 30.1 |

| DAC1 | 2 | 37.5 | 38.0 | 38.6 | 39.0 | 39.6 | 40.1 | 40.6 | 41.1 | 41.6 | 42.1 | 42.6 | 43.1 | 43.6 | 44.1 | 44.6 | 45.1 |