# SYNCHRONOUS DC/DC CONTROLLER FOR DISTRIBUTED POWER SUPPLY APPLICATIONS

September 5, 2000

TEL:805-498-2111 FAX:805-498-3804 WEB:http://www.semtech.com

## DESCRIPTION

The SC1102 is a low-cost, full featured, synchronous voltage-mode controller designed for use in single ended power supply applications where efficiency is of primary concern. Synchronous operation allows for the elimination of heat sinks in many applications. The SC1102 is ideal for implementing DC/DC converters needed to power advanced microprocessors in low cost systems, or in distributed power applications where efficiency is important. Internal level-shift, high-side drive circuitry, and preset shoot-thru control, allows the use of inexpensive N-channel power switches.

SC1102 features include temperature compensated voltage reference, triangle wave oscillator and current sense comparator circuitry. Power good signaling, shutdown, and over voltage protection are also provided.

The SC1102 operates at a fixed 200kHz, providing an optimum compromise between efficiency, external component size, and cost.

#### **FEATURES**

- 1.265V Reference available

- Synchronous operation

- Over current fault monitor

- On-chip power good and OVP functions

- Small size with minimum external components

- Soft Start

- R<sub>DS(ON)</sub> Current sensing

## **APPLICATIONS**

- Microprocessor core supply

- Low cost synchronous applications

- Voltage Regulator Modules (VRM)

### ORDERING INFORMATION

| DEVICE <sup>(1)</sup> | PACKAGE          | TEMP. RANGE (T <sub>J</sub> ) |  |

|-----------------------|------------------|-------------------------------|--|

| SC1102CSTR            | SO-14            | 0 - 125°C                     |  |

| SC1102EVB             | Evaluation Board |                               |  |

#### Note:

(1) Only available in tape and reel packaging. A reel contains 2500 devices.

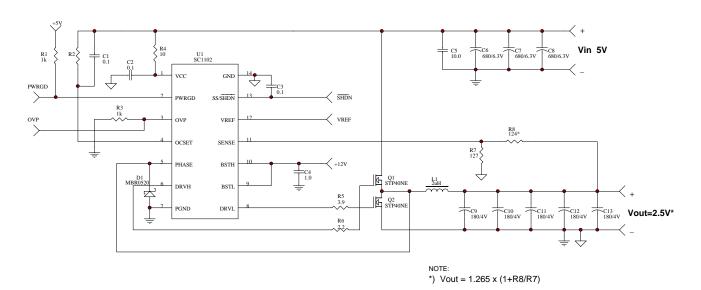

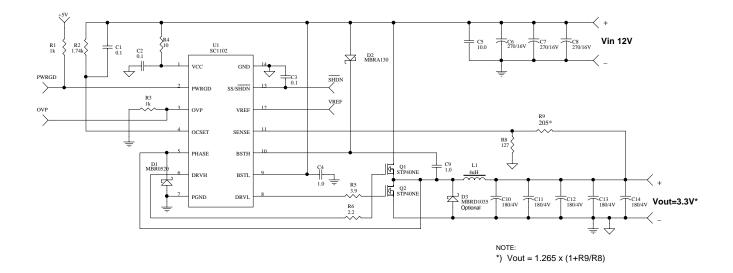

## **APPLICATION CIRCUIT**

#### **Typical Distributed Power Supply**

Figure 1.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                              | Symbol            | Maximum     | Units |

|----------------------------------------|-------------------|-------------|-------|

| V <sub>CC</sub> , BSTL to GND          | V <sub>IN</sub>   | -0.3 to 14  | V     |

| PGND to GND                            |                   | ± 0.5       | V     |

| PHASE to GND                           |                   | -0.3 to 18  | V     |

| BSTH to PHASE                          |                   | 14          | V     |

| Thermal Resistance Junction to Case    | $\theta_{\sf JC}$ | 45          | °C/W  |

| Thermal Resistance Junction to Ambient | $\theta_{JA}$     | 115         | °C/W  |

| Operating Temperature Range            | T <sub>A</sub>    | 0 to 70     | °C    |

| Storage Temperature Range              | T <sub>STG</sub>  | -65 to +150 | °C    |

| Lead Temperature (Soldering) 10 sec    | $T_{LEAD}$        | 300         | °C    |

| ESD Rating (Human Body Model)          | ESD               | 2           | kV    |

# **ELECTRICAL CHARACTERISTICS**

Unless specified:  $V_{CC} = 4.75V$  to 12.6V; GND = PGND = 0V;  $FB = V_O$ ;  $V_{BSTL} = 12V$ ;  $V_{BSTH-PHASE} = 12V$ ;  $T_J = 25^{\circ}C$

| PARAMETER                 | CONDITIONS                             | MIN | TYP | MAX  | UNITS |

|---------------------------|----------------------------------------|-----|-----|------|-------|

| POWER SUPPLY              |                                        |     |     |      |       |

| Supply Voltage            | V <sub>cc</sub>                        | 4.2 |     | 12.6 | V     |

| Supply Current            | EN = V <sub>CC</sub>                   |     | 6   | 10   | mA    |

| Line Regulation           | V <sub>O</sub> = 2.5V                  |     | 0.5 |      | %     |

| ERROR AMPLIFIER           |                                        |     |     |      |       |

| Gain (AOL)                |                                        |     | 35  |      | dB    |

| Input Bias                |                                        |     | 5   | 8    | μA    |

| OSCILLATOR                |                                        |     |     |      |       |

| Oscillator Frequency      |                                        | 180 | 200 | 220  | kHz   |

| Oscillator Max Duty Cycle |                                        | 90  | 95  |      | %     |

| MOSFET DRIVERS            |                                        |     |     |      |       |

| DH Source/Sink Current    | $BST_H - DH = 4.5V / DH - PHASE = 2V$  | 1   |     |      | А     |

| DL Source/Sink Current    | $BST_L - DL = 4.5V / DL - PGND_L = 2V$ | 1   |     |      | А     |

| PROTECTION                |                                        |     |     |      |       |

| OVP Threshold Voltage     |                                        |     | 20  |      | %     |

| OVP Source Current        | $V_{OVP} = 3V$                         | 10  |     |      | mA    |

| Power Good Threshold      |                                        | 88  |     | 112  | %     |

| Dead Time                 |                                        | 45  |     | 100  | ns    |

| Over Current Set Isource  | 2.0V ≤ V <sub>OCSET</sub> ≤ 12V        | 180 | 200 | 220  | μA    |

## NOTE:

(1) Specification refers to application circuit (Figure 1).

# **ELECTRICAL CHARACTERISTICS (CONT)**

Unless specified:  $V_{CC} = 4.75V$  to 12.6V; GND = PGND = 0V; FB =  $V_{O}$ ;  $V_{BSTL} = 12V$ ;  $V_{BSTH-PHASE} = 12V$ ;  $V_{LSTH-PHASE} = 12V$ ;  $V_{LST$

| PARAMETER         | CONDITIONS             | MIN   | TYP   | MAX   | UNITS |

|-------------------|------------------------|-------|-------|-------|-------|

| REFERENCE         |                        |       |       |       |       |

| Reference Voltage |                        | 1.252 | 1.265 | 1.278 | V     |

| Accuracy          |                        | -1    |       | +1    | %     |

| SOFT START        |                        |       |       |       |       |

| Charge Current    | V <sub>SS</sub> = 1.5V | 8.0   | 10    | 12    | μA    |

| Discharge Current | V <sub>SS</sub> = 1.5V | 1.3   | 2     | 2.4   | μA    |

## **PIN CONFIGURATION**

# Top View VCC 🖂 1 14 - GND 13 SS/SHDN 12 WREF OVP III 3 OCSET = 4 11 = SENSE PHASE □ 5 10 BSTH 9 BSTL DH □ 6 8 DL PGND 四7 (14-Pin SOIC)

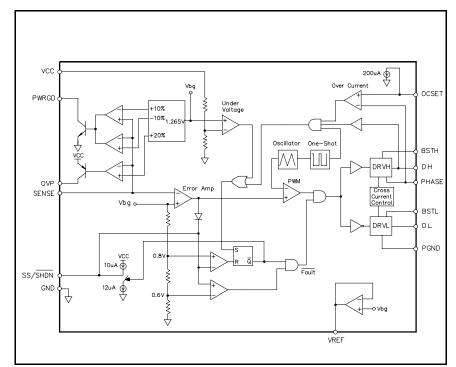

# **BLOCK DIAGRAM**

# PIN DESCRIPTION

| Pin# | Pin Name | Pin Function                                                |

|------|----------|-------------------------------------------------------------|

| 1    | VCC      | Chip supply voltage                                         |

| 2    | PWRGD    | Logic high indicates correct output voltage                 |

| 3    | OVP      | Over voltage protection.                                    |

| 4    | OCSET    | Sets the converter overcurrent trip point                   |

| 5    | PHASE    | Input from the phase node between the MOSFET'S              |

| 6    | DH       | High side driver output                                     |

| 7    | PGND     | Power ground                                                |

| 8    | DL       | Low side driver output                                      |

| 9    | BSTL     | Bootstrap, low side driver.                                 |

| 10   | BSTH     | Bootstrap, high side driver.                                |

| 11   | SENSE    | Voltage sense input                                         |

| 12   | VREF     | Buffered band gap voltage reference.                        |

| 13   | SS/SHDN  | Soft start. A capacitor to ground sets the slow start time. |

| 14   | GND      | Signal ground                                               |

## NOTE:

(1) All logic level inputs and outputs are open collector TTL compatible.

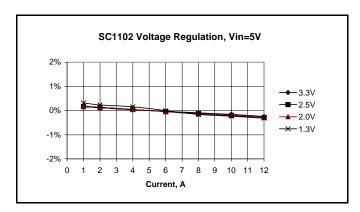

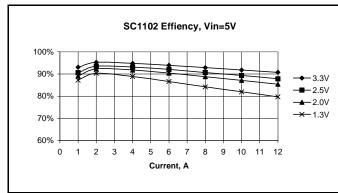

# **CHARACTERISTIC CURVES**

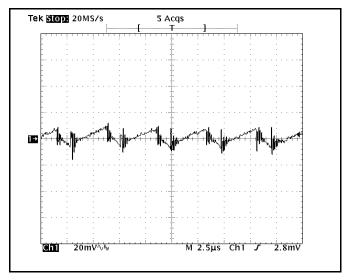

# **Output Ripple Voltage**

# 1. $V_{IN} = 5V$ ; $V_{O} = 3.3V$ ; $I_{OUT} = 12A$

Ch1: Vo\_rpl

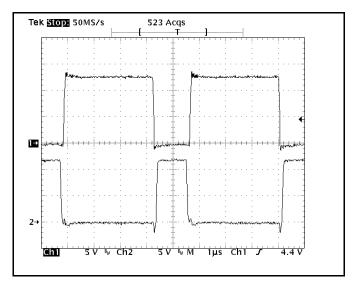

#### **Gate Drive Waveforms**

Ch1: Top FET Ch2: Bottom FET

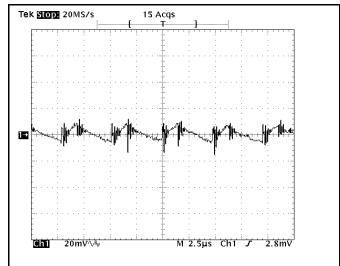

# 2. $V_{IN} = 5V$ ; $V_{OUT} = 1.3V$ ; $I_{OUT} = 12A$

Ch1: Vo\_rpl

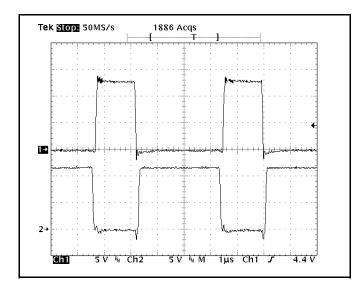

Ch1: Top FET Ch2: Bottom FET

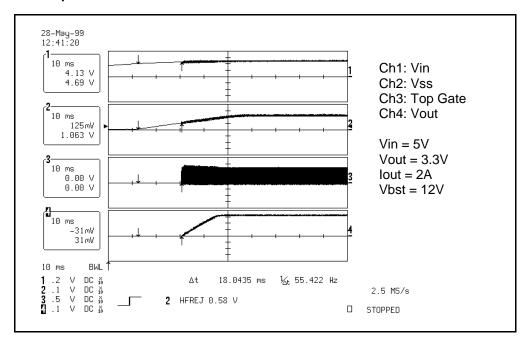

# Start Up

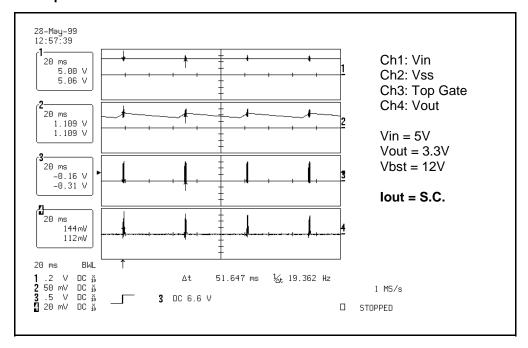

## **Hiccup Mode**

# SYNCHRONOUS DC/DC CONTROLLER FOR DISTRIBUTED POWER SUPPLY APPLICATIONS

September 5, 2000

#### THEORY OF OPERATION

#### **Synchronous Buck Converter**

Primary  $V_{\text{CORE}}$  power is provided by a synchronous, voltage-mode pulse width modulated (PWM) controller. This section has all the features required to build a high efficiency synchronous buck converter, including "Power Good" flag, shut-down, and cycle-by-cycle current limit.

The output voltage of the synchronous converter is set and controlled by the output of the error amplifier. The external resistive divider reference voltage is derived from an internal trimmed-bandgap voltage reference (See Fig. 1). The inverting input of the error amplifier receives its voltage from the SENSE pin.

The internal oscillator uses an on-chip capacitor and trimmed precision current sources to set the oscillation frequency to 200kHz. The triangular output of the oscillator sets the reference voltage at the inverting input of the comparator. The non-inverting input of the comparator receives it's input voltage from the error amplifier. When the oscillator output voltage drops below the error amplifier output voltage, the comparator output goes high. This pulls DL low, turning off the low-side FET, and DH is pulled high, turning on the high-side FET (once the cross-current control allows it). When the oscillator voltage rises back above the error amplifier output voltage, the comparator output goes low. This pulls DH low, turning off the high-side FET, and DL is pulled high, turning on the low-side FET (once the cross-current control allows it).

As SENSE increases, the output voltage of the error amplifier decreases. This causes a reduction in the ontime of the high-side MOSFET connected to DH, hence lowering the output voltage.

#### **Under Voltage Lockout**

The under voltage lockout circuit of the SC1102 assures that the high-side MOSFET driver outputs remain in the off state whenever the supply voltage drops below set parameters. Lockout occurs if  $V_{\rm CC}$  falls below 4.1V. Normal operation resumes once  $V_{\rm CC}$  rises above 4.2V.

#### **Over-Voltage Protection**

The over-voltage protection pin (OVP) is high only when the voltage at SENSE is 20% higher than the target value programmed by the external resistor divider. The OVP pin is internally connected to a PNP's collector.

#### **Power Good**

The power good function is to confirm that the regulator outputs are within +/-10% of the programmed level. PWRGD remains high as long as this condition is met. PWRGD is connected to an internal open collector NPN transistor.

#### **Soft Start**

Initially, SS/SHDN sources  $10\mu A$  of current to charge an external capacitor. The outputs of the error amplifiers are clamped to a voltage proportional to the voltage on SS/SHDN. This limits the on-time of the high-side MOSFETs, thus leading to a controlled ramp-up of the output voltages.

# R<sub>DS(ON)</sub> Current Limiting

The current limit threshold is set by connecting an external resistor from the  $V_{\rm CC}$  supply to OCSET. The voltage drop across this resistor is due to the 200 $\mu$ A internal sink sets the voltage at the pin. This voltage is compared to the voltage at the PHASE node. This comparison is made only when the high-side drive is high to avoid false current limit triggering due to uncontributing measurements from the MOSFET's off-voltage. When the voltage at PHASE is less than the voltage at OCSET, an overcurrent condition occurs and the soft start cycle is initiated. The synchronous switcher turns off and SS/SHDN starts to sink 2 $\mu$ A. When SS/SHDN reaches 0.8V, it then starts to source 10 $\mu$ A and a new cycle begins.

#### **Hiccup Mode**

During power up, the SS/S $\overline{\text{HDN}}$  pin is internally pulled low until VCC reaches the undervoltage lock-out level of 4.2V. Once  $V_{CC}$  has reached 4.2V, the SS/S $\overline{\text{HDN}}$  pin is released and begins to source 10 $\mu$ A of current to the external soft-start capacitor. As the soft-start voltage rises, the output of the internal error amplifier is clamped to this voltage. When the error signal reaches the level of the internal triangular oscillator, which swings from 1V to 2V at a fixed frequency of 200 kHz, switching occurs. As the error signal crosses over the oscillator signal, the duty cycle of the PWM signal continues to increase until the output comes into regulation. If an over-current condition has not occurred the soft-start voltage will continue to rise and level off at about 2.2V.

# SYNCHRONOUS DC/DC CONTROLLER FOR DISTRIBUTED POWER SUPPLY APPLICATIONS

September 5, 2000

# THEORY OF OPERATION (CON'T)

An over-current condition occurs when the high-side drive is turned on, but the PHASE node does not reach the voltage level set at the OCSET pin. The PHASE node is sampled only once per cycle during the valley of the triangular oscillator. Once an over-current occurs, the high-side drive is turned off and the low-side drive turns on and the SS/SHDN pin begins to sink 2uA. The soft-start voltage will begin to decrease as the 2uA of current discharges the external capacitor. When the soft-start voltage reaches 0.8V, the SS/SHDN pin will begin to source 10uA and begin to charge the external capacitor causing the soft-start voltage to rise again. Again, when the soft-start voltage reaches the level of the internal oscillator, switching will occur.

If the over-current condition is no longer present, normal operation will continue. <u>If the</u> over-current condition is still present, the SS/SHDN pin will again begin to sink 2uA. This cycle will continue indefinitely until the over-current condition is removed.

In conclusion, below is shown a typical "12V Application Circuit" which has a BSTH voltage derived by bootstrapping input voltage to the PHASE node through diode D1. This circuit is very useful in cases where only input power of 12V is available.

In order to prevent substrate glitching, a small-signal diode should be placed in close proximity to the chip with cathode connected to PHASE and anode connected to PGND.

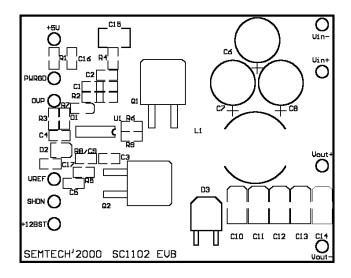

## **APPLICATION CIRCUIT**

Typical 12V Application Circuit with Bootstrapped BSTH

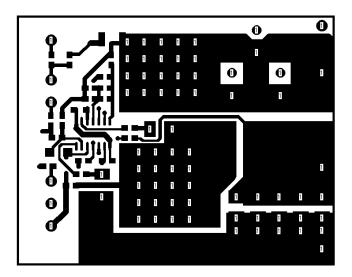

Top component side view

Top copper view

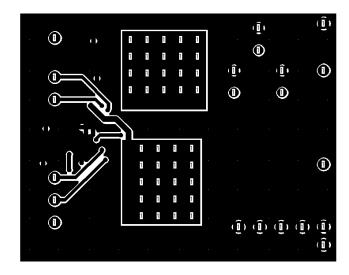

Bottom copper view

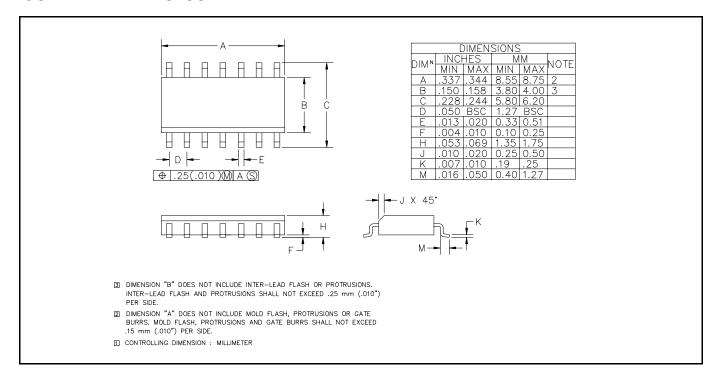

## **OUTLINE DRAWING SO-14**

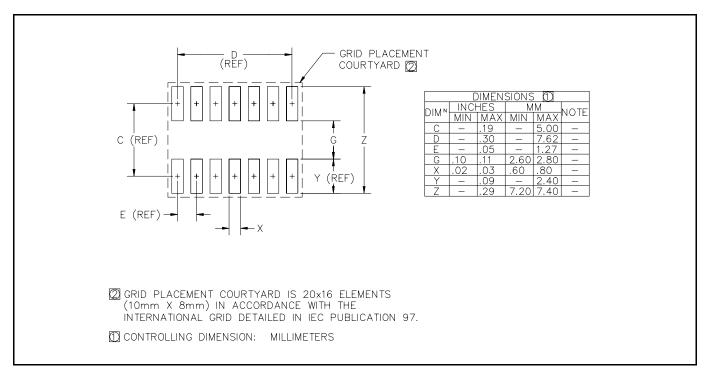

# **LAND PATTERN SO-14**

ECN00-1311

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.