PRELIMINARY DATA SHEET

SDA 9488X PIP IV Basic SDA 9588X OCTOPUS Cost-effective Picture-In-Picture ICs

# Cost effective Picture-In-Picture (PIP) ICs

Version 1.3 CMOS

## **General Description**

SDA 9488X 'PIP IV Basic' and SDA 9588X 'OCTOPUS' belong to a new generation of costeffective PiP processors that combine high-quality digital PIP signal processing, digital multistandard color decoding and AD/DA conversion on a single chip. Both devices are equipped with CVBS and Y/C input interfaces. In addition the SDA 9588X is also able to process YUV input signals for displaying high-quality video signals e.g. coming from a DVD source.

Figure 0-1 Picture-In-Picture

The integrated digital color decoder is able to decode all analog TV standards (PAL, NTSC and SECAM) and detects the standard automatically. Therefore the IC is suited for world-wide use.

A picture reduction from 1/9 to 1/81 of original size selectable in fine steps is possible. The transfer functions of the decimation filters are optimally matched to the selected picture size reduction and can furthermore be adjusted to the viewer's requirements by a selectable peaking. A maximum of 216 luminance and 2x54 chrominance pixels per line are stored in the memory.

| Туре      | Package   |

|-----------|-----------|

| SDA 9488X | P-DSO28-1 |

| SDA 9588X | P-DSO28-1 |

# **SDA 9588X**

| 1      | Features                                       | 5  |

|--------|------------------------------------------------|----|

| 2      | Pin Configuration                              | 7  |

| 3      | Block Diagram                                  | 9  |

| 4      | System Description                             | 10 |

| 4.1    | Analog Frontend                                | 10 |

| 4.1.1  | Input Selection                                | 10 |

| 4.1.2  | AD-Conversion                                  | 10 |

| 4.1.3  | Automatic Gain Control                         | 11 |

| 4.1.4  | Signal Magnitudes                              | 11 |

| 4.2    | Inset Synchronization                          | 13 |

| 4.3    | Chroma Decoding And Standard Search            | 13 |

| 4.4    | Comb Filtering                                 | 15 |

| 4.5    | Luminance Processing                           | 15 |

| 4.6    | Decimation                                     | 16 |

| 4.6.1  | Single PIP Mode                                | 16 |

| 4.6.2  | Horizontal And Vertical Fine Positioning       | 19 |

| 4.6.3  | Multi Display Mode                             | 19 |

| 4.7    | Display Control                                | 20 |

| 4.7.1  | Mixed Standard Applications And (S)VGA Support | 23 |

| 4.7.2  | Display standard                               | 24 |

| 4.7.3  | Picture Positioning                            | 25 |

| 4.8    | Output Signal Processing                       | 26 |

| 4.8.1  | Luminance Peaking                              | 26 |

| 4.8.2  | RGB Matrix                                     |    |

| 4.8.3  | Framing And Colored Background                 | 27 |

| 4.8.4  | 16:9 Inset Picture Support                     |    |

| 4.8.5  | Parent Clock Generation                        | 29 |

| 4.8.6  | Select Signal                                  |    |

| 4.9    | DA-Conversion And RGB / YUV Switch             |    |

| 4.9.1  | Contrast, Brightness and Peak Level Adjustment |    |

| 4.9.2  | Pedestal Level Adjustment                      |    |

| 4.10   | Data Slicer                                    |    |

| 4.10.1 | Closed Caption                                 |    |

| 4.10.2 | Widescreen Signalling (WSS)                    |    |

| 4.10.3 | Indication Of New Data                         |    |

| 4.10.4 | Violence Protection                            | 35 |

| 5      | Application Examples                           | 36 |

| 6      | I2C Bus                                        | 37 |

| 6.1    | I2C Bus Address                                | 37 |

| 6.2    | I2C-Bus Format                                 | 37 |

# **SDA 9588X**

| 6.3<br>6.4 | I2C bus Command Table       |    |

|------------|-----------------------------|----|

| 7          | Pin Description             |    |

| 8          | Absolute Maximum Ratings    | 71 |

| 9          | Recommended Operating Range | 72 |

| 10         | Characteristics             | 76 |

| 11         | Diagrams                    | 80 |

| 12         | Application Circuit         | 86 |

**Features**

#### 1 Features

- Single chip solution:

- AD-conversion for CVBS or Y/C or YUV<sup>1)</sup>, multistandard color decoding, PLL for synchronization of inset channel, decimation filtering, embedded memory, RGBmatrix, DA-conversion, RGB/YUV switch, data-slicer and clock generation integrated on chip

- · Analog inputs:

- 3x CVBS or 1x CVBS and 1x Y/C or 1xYUV (SDA 9588X) alternatively

- Clamping of each input

- All ADCs with 8 bit amplitude resolution

- Automatic Gain Control (AGC) for Y and CVBS

- Inset Synchronization:

- Multiple time constants for reliable synchronization

- Automatic recognition of 625 lines / 525 lines standard

- · Color Decoder:

- PAL-B/G, PAL-M, PAL-N(Argentina), PAL60, NTSC-M, NTSC4.4 and SECAM

- Adjustable color saturation

- Hue control for NTSC

- Automatic Chroma Control (-24 dB ... +6 dB)

- Automatic recognition of chroma standards: different search strategies selectable

- Single crystal for all standards

- IF-characteristic compensation filter

- Decimation:

- PIP sizes between 1/81 and 1/9 adjustable with steps of 2 lines and 4 pixel

- Resolution up to 216 luminance and 2x54 chrominance pixels per inset line

- Horizontal and vertical filtering dependent on picture size

- · Display Features:

- 7 bit per pixel stored in memory

- Field and joint-line free frame mode display

- Display on VGA and SVGA screen (f<sub>H</sub> limited to 40kHz)

- 8 different read frequencies for 16:9 compatibility

- Line doubling mode for progressive scan applications

- Freeze picture

- Coarse positioning at 4 corners of the parent picture

- Fine positioning at steps of 4 pixels and 2 lines

- · Output signal processing:

- 7 Bit DAC

- RGB or YUV switch: insertion of an external source without PIP processing

- Digital interpolation for anti-imaging

<sup>1)</sup> available with SDA 9588X only

#### **SDA 9588X**

**Features**

- Adjustable transient improvement for luma (peaking)

- Contrast, Brightness and Pedestal Level adjustable

- Analog outputs: Y, +(B-Y), +(R-Y), or Y, -(B-Y), -(R-Y) or RGB

- Three RGB matrices available: NTSC(Japan), NTSC(USA) or EBU

- 64 different background colors and 4096 different frame colors

- Plain or 3D frame with variable width and height

- · Data Slicing:

- Slicing of closed-caption (CC) or wide-screen-signaling (WSS) data

- Violence blocking capability (V-chip)

- Several filter for XDS data extraction

- I<sup>2</sup>C-Bus control (400 kHz)

- High stability clock generation

- PDSO 28-1 package (SMD)

- Full SDA 9489X and SDA 9589X upward compatibility

- SDA 9388X / SDA 9389X pinout compatibility

- 3.3V supply voltage (5V input capable)

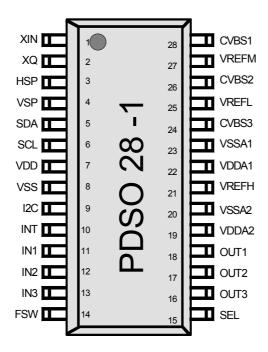

# 2 Pin Configuration

Figure 2-1 Pinning

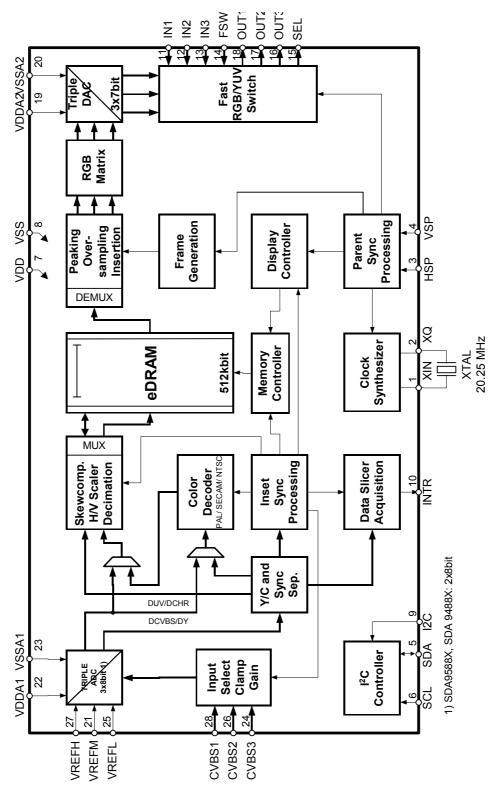

- 1) Does not include plastic or metal protrusion of 0.15 max. per side

- 2) Does not include dambar protrusion of 0.05 max. per side

Figure 2-2 Package Outlines

# Pin Configuration

| Numb<br>er | Name    | Туре         | Description                                             |

|------------|---------|--------------|---------------------------------------------------------|

| 1          | XIN     | I            | crystal oscillator (input) or external clock input      |

| 2          | XQ      | 0            | crystal oscillator (output)                             |

| 3          | HSP     | I/TTL        | horizontal sync for parent channel                      |

| 4          | VSP     | I/TTL        | vertical sync for parent channel                        |

| 5          | SDA     | I/O          | I <sup>2</sup> C-bus data                               |

| 6          | SCL     | I            | I <sup>2</sup> C-bus clock                              |

| 7          | VDD     | S            | digital supply voltage                                  |

| 8          | VSS     | S            | digital ground                                          |

| 9          | I2C     | I            | I <sup>2</sup> C Address                                |

| 10         | INT     | O/TTL        | interrupt                                               |

| 11         | IN1     | I/ana        | V/R input for external YUV/RGB source                   |

| 12         | IN2     | I/ana        | Y/G input for external YUV/RGB source                   |

| 13         | IN3     | I/ana        | U/B input for external YUV/RGB source                   |

| 14         | FSW     | I            | fast switch input for YUV/RGB switch                    |

| 15         | SEL     | 0            | fast blanking output for PIP                            |

| 16         | OUT3    | O/ana        | analog output: chrominance signal +(B-Y) or -(B-Y) or B |

| 17         | OUT2    | O/ana        | analog output: luminance signal Y or G                  |

| 18         | OUT1    | O/ana        | analog output: chrominance signal +(R-Y) or -(R-Y) or R |

| 19         | VDDA2   | S            | analog supply voltage for DAC                           |

| 20         | VSSA2   | S            | analog ground for DAC                                   |

| 21         | VREFH   | I/ana        | uppper reference voltage for ADC and DAC                |

| 22         | VDDA1   | S            | analog supply voltage for ADC                           |

| 23         | VSSA1   | S            | analog ground for ADC                                   |

| 24         | CVBS3   | I/ana        | CVBS3 or V (SDA 9588X) or C Input                       |

| 25         | VREFL   | I/O          | lower reference voltage for ADC                         |

| 26         | CVBS2   | I/ana        | CVBS2 or U (SDA 9588X) or Y (of Y/C) Input              |

| 27         | VREFM   | I/O          | mid-level reference voltage for ADC                     |

| 28         | CVBS1   | I/ana        | CVBS1 or Y (of YUV, SDA 9588X) Input                    |

|            | l= Inpu | t / ana=anal | og / O= Output / TTL=Digital (TTL) / S=Supply voltage   |

**Table 2-1 Pin Description**

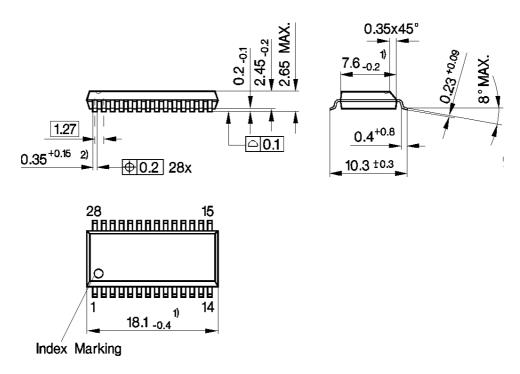

**Block Diagram**

# 3 Block Diagram

Figure 3-1 Block Diagram

# 4 System Description

# 4.1 Analog Frontend

## 4.1.1 Input Selection

An analog inset CVBS signal can be fed to the inputs CVBS1-3 of SDA 9588X resp. SDA 9488X. Each of these sources is selectable via I<sup>2</sup>C bus (**CVBSEL**). CVBS2 and CVBS3 can be used as separate Y/C inputs. YUV sources can be connected to CVBS1, CVBS2 and CVBS3 provided YUV operation at the SDA 9588X being enabled (**YUVSEL**). Using an external switch the SDA 9588X can operate in applications with both YUV and CVBS signals.

| CVE | SEL | YUVSEL | Input   |         |        | remark                       |

|-----|-----|--------|---------|---------|--------|------------------------------|

| D1  | D0  |        | CVBS1   | CVBS2   | CVBS3  |                              |

| 0   | 0   | 0      | CVBS    |         |        |                              |

| 0   | 1   | 0      |         | CVBS    |        |                              |

| 1   | 0   | 0      |         | Y (VBS) | С      | Y/C mode                     |

| 1   | 1   | 0      |         |         | CVBS   |                              |

| X   | Х   | 1      | Y (VBS) | U (CB)  | V (CR) | YUV mode<br>(SDA 9588X only) |

Table 4-1 Input selection

#### 4.1.2 AD-Conversion

All signal are clamped and AD-converted with an amplitude resolution of 8bit. CVBS and Y signals are clamped to the sync bottom whereas U/V and C signals are clamped to their mid-level during blanking.

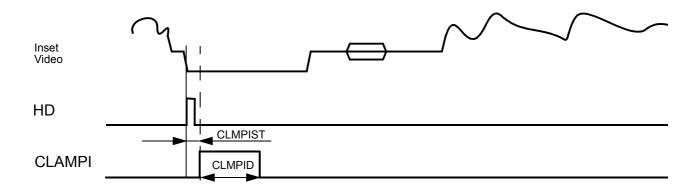

Figure 4-1 Clamping timing

The clamping pulse can be shifted in position (**CLMPIST**) and length (**CLMPID**) to adjust to the specific application. The ADCs are driven by a 20.25 MHz free running crystal clock which is not related to the incoming CVBS signal.

To avoid aliasing by subsampling the CVBS signal and the Y/C signals should be bandlimited to 10MHz. In the same manner the U/V signal frequency spectrum (SDA 9588X) should not exceed 5 MHz. The digital filtering suppresses all frequencies above the useable spectrum.

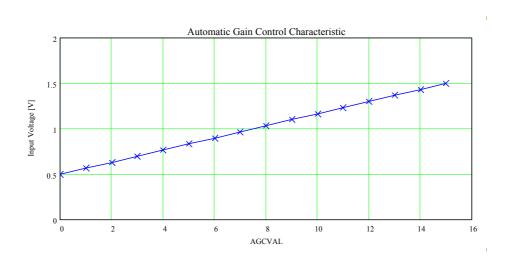

#### 4.1.3 Automatic Gain Control

To accommodate to different CVBS input voltages an automatic gain control has been implemented. The chip works correctly for input voltages in the range from 0.5 to  $1.5V_{pp}$ . For best signal-to-noise ratio, the maximum CVBS amplitude is recommended if available. The AGC behavior can be chosen out of four possibilities (**AGCMDE**):

The sync height serves as reference for the gain control in the typical application. When using overflow detection only, the gain is set to maximum and is reduced whenever an overflow occurs. This procedure will be executed again when a channel change is detected or the gain control is manually reset by **AGCRES**.

Figure 4-2 AGC characteristic

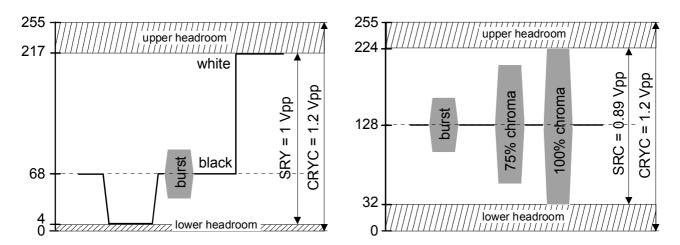

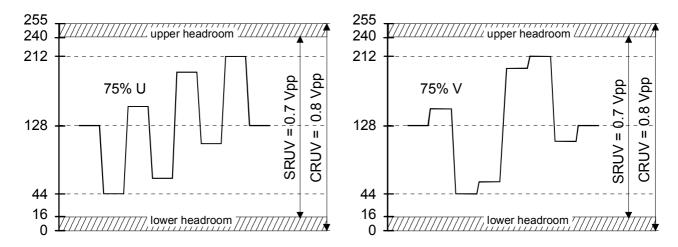

#### 4.1.4 Signal Magnitudes

The nominal CVBS signal with 75% color has a magnitude of 1  $V_{pp}$ . The upper headroom is left to permit signals with 100% color resulting in 1.23  $V_{pp}$ . The Y signal must always contain the sync part. Its levels correspond to the CVBS levels except for the missing color and burst. After A/D conversion the video part is clamped to its black value and is amplified to 224 digital steps. The nominal signal levels ensure correct brightness and saturation. The YUV signal levels conform to the ITU 601 recommendation.

Figure 4-3 CVBS/Y and chroma ADC input signal range

Figure 4-4 UV input signal range

| AGCVAL |    | Conversion | Signal | Signal             | Conversion          | Signal              |                    |                    |  |

|--------|----|------------|--------|--------------------|---------------------|---------------------|--------------------|--------------------|--|

| D3     | D2 | D1         | D0     | Range<br>CRYC      | Range<br>SRY        | Range<br>SRC        | Range<br>CRUV      | Range<br>SRUV      |  |

| 0      | 0  | 0          | 0      | $0.5V_{pp}$        | 0.42V <sub>pp</sub> |                     |                    |                    |  |

|        |    |            |        | •••                |                     |                     |                    |                    |  |

| 1      | 0  | 0          | 0      | 1.2V <sub>pp</sub> | 1.0V <sub>pp</sub>  | 0.89V <sub>pp</sub> | 0.8V <sub>pp</sub> | 0.7V <sub>pp</sub> |  |

|        |    |            |        |                    |                     |                     |                    |                    |  |

| 1      | 1  | 1          | 1      | 1.5V <sub>pp</sub> | 1.25V <sub>pp</sub> |                     |                    |                    |  |

Table 4-2 ADC conversion range and required input signal voltage

# 4.2 Inset Synchronization

Horizontal and vertical sync pulses are separated after elimination of the high frequency components of the CVBS signal by a low pass filter. Horizontal sync pulses are generated by a digital phase-locked-loop (DPLL). Its time constant is adjustable between fast and slow behavior in four steps (**PLLITC**) to consider different input sources (e.g. VCR). Noisy input signals become more stable when a noise-reduction is enabled (**NSRED**). Additionally weak input signals from a satellite dish ('fishes') become more stable when **SATNR** is enabled. Both should be enabled to have best available performance. When **NOSIGB** is enabled, a colored background is shown instead of the picture when PIP is out of synchronization. The detected line standard is indicated by **SYNCSTAT**.

## 4.3 Chroma Decoding And Standard Search

The system is able to decode NTSC and PAL signals with a subcarrier of 3.58MHz and 4.43MHz (PAL B/M/N/60, NTSC M/4.4) as well as SECAM signals with 4.05/4.2MHz subcarrier. The system may be forced to a certain standard, or an automatic standard detection can be used (**CSTAND**). For automatic standard detection, some standards which are not likely to be received can be ignored to improve the detection process.

Depending on the detected line standard (525 or 625 lines) the color standard detection circuit searches for 60 Hz signals (NTSC-M / PAL-M / PAL 60 / NTSC44) or 50 Hz signals (PAL-B / SECAM / PAL-N) respectively. Within each line standard, the standard is detected by consequently switching from one to another. This standard detection process can be set to medium or fast behavior (LOCKSP). In medium behavior 30 fields (in fast 20) are used to detect the standard. If not being successful within this time period the system tries to detect another one. For SECAM detection, a choice between two recognition levels is possible (SCMIDL) and the evaluated burstposition is selectable (BGPOS).

| CSTA | NDEX | NTSC- | PAL60 | PAL-N | PAL-M | PAL-B | SECAM | NTSC |

|------|------|-------|-------|-------|-------|-------|-------|------|

| D1   | D0   | M     |       |       |       |       |       | 44   |

| 0    | 0    |       |       |       |       |       |       |      |

| 0    | 1    |       |       |       |       |       |       |      |

| 1    | 0    |       |       |       |       |       |       |      |

| 1    | 1    |       |       |       |       |       |       |      |

Table 4-3 Considered color standards for automatic standard detection

For getting the chrominance information the digitized video signal is multiplied with the regenerated color subcarrier once in-phase and once phase-shifted by 90°. After lowpass filtering digital UV is available for PAL and NTSC. The subcarrier is regenerated

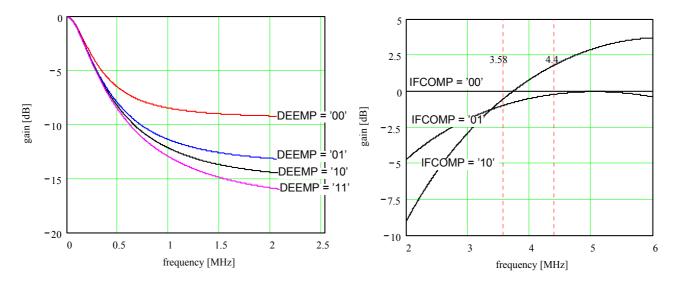

by a digital PLL. At SECAM operation the PLL runs free and generates the line-wise alternating subcarriers. A CORDIC structure demodulates the frequency-modulated UV signals. The following SECAM de-emphasis filter characteristic is adjustable (**DEEMP**).

The chroma signal can be filtered before demodulation by means of a selectable IF-prefilter (**IFCOMP**).

Figure 4-5 SECAM de-emphasis filter characteristic and IF-compensation filter characteristic

The Hue Control (**HUE**) influences the phase of the demodulation subcarrier between -44.8° and 43.4° in steps of 1.4°. This is provided for NTSC only and adjustment is ineffective for PAL and SECAM signals.

The reference for the subcarrier generation is a crystal stable clock of 20.25000 MHz. In order to avoid color standard detection problems, the maximum deviation of this frequency should not exceed 100ppm. For a good PLL locking behavior a maximum deviation of 40ppm is recommended. A small frequency adjustment (-150 ... +310 ppm) is possible for using a crystal with small frequency deviations (SCADJ). For test purposes, CPLL allows to open the loop of the chroma PLL.

For deviations in the chroma signal up to 30dB, a stable output amplitude after chroma decoding is achieved due to the ACC (Automatic Chroma Control). If the chroma signal (color burst) is below a selectable threshold (**CKILL**), the color will be switched off. Alternatively the color-killer can be bypassed and the color can be switched on or off under all conditions (**COLON**). By setting **ACCFIX**, the automatic chroma control is disabled and set to a default value.

| CKILL |    | COLON | color killed at damping of |  |  |  |

|-------|----|-------|----------------------------|--|--|--|

| D1    | D0 |       |                            |  |  |  |

| 0     | 0  | 0     | 30 dB                      |  |  |  |

| 0     | 1  | 0     | 18 dB                      |  |  |  |

| 1     | 1  | 0     | 24 dB                      |  |  |  |

| 1     | 1  | 0     | color always off           |  |  |  |

| Х     | Х  | 1     | color always on            |  |  |  |

# Table 4-4 Color-killer adjustment

The bandwidth of the chroma filter is adjustable via **CHRBW**. The bandwidth depends on whether the decoder is in SECAM operation or not. A change in **CHRBW** does not result in a chrominance position shift on the screen.

**CKSTAT** can be read out and gives information whether the color is switched on or off. **STDET** indicates the detected color standard. Additionally **PALID** signals whether a PAL signal or a NTSC signal is applied.

# 4.4 Comb Filtering

Depending on the selected picture size and color standard, a comb filtering is performed for luminance and chrominance. A comb filter uses the spectral interleaving of the encoded luminance and chrominance to separate both without cross artifacts. Thus cross-color and cross-luminance are suppressed effectively. For NTSC sources, a comb filtering is performed for all picture sizes. Due to reduced bandwidth in horizontal and vertical direction a strong reduction of cross artifacts can be achieved for PAL signals. The same applies for the luminance signal of SECAM signals.

## 4.5 Luminance Processing

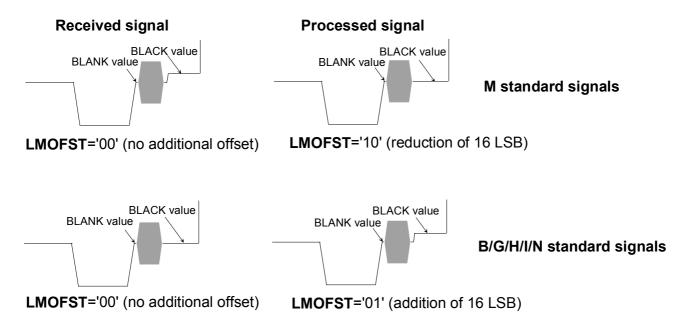

The A/D-converted CVBS (or Y) signal is digitally clamped to back porch. Depending on the transmitted standard and operational area, an offset between black- and blanking level can be found in the incoming signal ('7.5 IRE'). As for some applications a black offset is not desired, controlling may be done using **LMOFST**. The positive or negative offset is added to the Y signal before scaling.

Figure 4-6 Black level correction of luminance signal

The color carrier is removed out of a CVBS signal by means of a notch filter. It is set to the corresponding color carrier (3.58 or 4.4 MHz) only if the standard is detected permanently. This prevents the luminance sharpness of being changed within the standard search process. For Y signals the notch is disabled.

For a fine adjustment of delaycompensation between luminance and chrominance, **YCDEL** allows a luminance shifting in 16 steps of 50ns.

#### 4.6 Decimation

#### 4.6.1 Single PIP Mode

Luminance and chrominance signals are filtered in horizontal and vertical direction. The coarse horizontal and vertical picture size (1/3, 1/4, 1/6) is independently programmable with **SIZEHOR** and **SIZEVER**. A fine adjustment in steps of 4 pixel and 2 lines is possible by **HSHRINK** and **VSHRINK**, which allows correct aspect ratio for multistandard applications (50/60 Hz mixed mode, (S)VGA).

For main decimation factors, the stored number of pixel and lines are listed in the following tables.

| SIZEHOR |    | horizontal        | PIP Pixel per line |       |       |  |  |

|---------|----|-------------------|--------------------|-------|-------|--|--|

| D1      | D0 | scaling           | Y                  | (B-Y) | (R-Y) |  |  |

| 0       | 0  | 3:1 <sup>1)</sup> | 216                | 54    | 54    |  |  |

| 0       | 1  | 3:1               | 216                | 54    | 54    |  |  |

| 1       | 0  | 4:1               | 160                | 40    | 40    |  |  |

| 1       | 1  | 6:1               | 108                | 27    | 27    |  |  |

<sup>1)</sup> only used for compatiblity with other SDA 948xX/958xX types

Table 4-5 Number of stored pixel per line dependent on SIZEHOR

| SIZE | VER             | vertical scaling | PIP lines        |                  |

|------|-----------------|------------------|------------------|------------------|

| D1   | D0              |                  | 625 lines source | 525 lines source |

| 0    | O <sup>1)</sup> | 3:1              | 88               | 72               |

| 0    | 1               | 3:1              | 88               | 72               |

| 1    | 0               | 4:1              | 66               | 54               |

| 1    | 1               | 6:1              | 44               | 36               |

<sup>1)</sup> only used for compatibility with other SDA 948xX/958xX types

Table 4-6 Number of stored lines per field

| HSHRNK           | SIZEHOR          | Decimation<br>factor                                         | stored Pixel                    | HSHRNK      | SIZEHOR                                   | Decimation<br>factor | stored Pixel |

|------------------|------------------|--------------------------------------------------------------|---------------------------------|-------------|-------------------------------------------|----------------------|--------------|

| 0                | 1                | 3,00                                                         | 216                             | 0           | 3                                         | 6,00                 | 108          |

| 1                | 1                | 3,04                                                         | 212                             | 1           | 3                                         | 6,23                 | 104          |

| 2                | 1                | 3,11                                                         | 208                             | 2           | 3                                         | 6,48                 | 100          |

| 3                | 1                | 3,17<br>3,23<br>3,29                                         | 212<br>208<br>204<br>200        | 3           |                                           | 6.75                 | 96           |

| 4                | 1                | 3,23                                                         | 200                             | 4           | 3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | 7,04<br>7,35<br>7,70 | 92           |

| 5                | 1                | 3,29                                                         | 196                             | 5<br>6<br>7 | 3                                         | 7,35                 | 88           |

| 6                | 1                | 3,37                                                         | 192                             | 6           | 3                                         | 7,70                 | 84           |

| 7                | 1                | 3,44                                                         | 188                             |             | 3                                         | 8,10                 | 80           |

| 8                | 1                | 3,51<br>3,60                                                 | 184                             | 8           | 3                                         | 8,52                 | 76           |

| 9                | 1                | 3,60                                                         | 180                             | a           | 3                                         | 8,99                 | 72           |

| 10               | 1                | 3,67                                                         | 176                             | 10          | 3                                         | 9,51                 | 68           |

| 11               | 1                | 3,76                                                         | 172                             | 11<br>12    | 3                                         | 10,12                | 64<br>60     |

| 12               | 1                | 3,84                                                         | 172<br>168                      | 12          | 3                                         | 10,12<br>10,64       | 60           |

| 13               | 1                | 3,94<br>4,05<br>4,16<br>4,27<br>4,38<br>4,50<br>4,63<br>4,77 | 164<br>160<br>156<br>152        |             |                                           |                      |              |

| 0                | 2                | 4,05                                                         | 160                             |             |                                           |                      |              |

| 1                | 2                | 4,16                                                         | 156                             |             |                                           |                      |              |

| 2                | 2                | 4,27                                                         | 152                             |             |                                           |                      |              |

| 2<br>3<br>4<br>5 | 2<br>2<br>2<br>2 | 4,38                                                         | 148<br>144<br>140<br>136<br>132 |             |                                           |                      |              |

| 4                | 2                | 4,50                                                         | 144                             |             |                                           |                      |              |

| 5                | 2                | 4,63                                                         | 140                             |             |                                           |                      |              |

| 6                | 2                | 4,77                                                         | 136                             |             |                                           |                      |              |

| 7                | 2<br>2<br>2      | 4,91                                                         | 132                             |             |                                           |                      |              |

| 8                | 2                | 5,06                                                         | 128                             |             |                                           |                      |              |

| 9                | 2                | 5,22                                                         | 124                             |             |                                           |                      |              |

| 10               | 2                | 5,22<br>5,41                                                 | 124<br>120                      |             |                                           |                      |              |

| 11               | 2                | 5,59                                                         | 116                             |             |                                           |                      |              |

| 12               | 2                | 5,78                                                         | 112                             |             |                                           |                      |              |

Table 4-7 Number of stored pixel per line dependent on HSHRNK

Lines

36

34

32

30

28

26

24

22

20

525 lines

Dec. Factor

6,00

6,38

6,75

7,22

7,73

8,30

9,00

9,80

28 10,78

ines

44

42

40

38

36

34

32

30

26 24

|        |         | 625 lin     | es    | 525 li      | nes   |        |         | 625 line    | es   |

|--------|---------|-------------|-------|-------------|-------|--------|---------|-------------|------|

| VSHRNK | SIZEVER | Dec. Factor | Lines | Dec. Factor | Lines | VSHRNK | SIZEVER | Dec. Factor | sau! |

| 0      | 1       | 3,00        | 88    | 3           | 72    | 0      | 3       | 6,00        | 4    |

| 1      | 1       | 3,07        | 86    | 3,09        | 70    | 1      | 3       | 6,28        | 4    |

| 2      | 1       | 3,14        | 84    | 3,19        | 68    | 2      | 3       | 6,61        | 4    |

| 3      | 1       | 3,21        | 82    | 3,28        | 66    | 3      | 3       | 6,94        | (    |

| 4      | 1       | 3,30        | 80    | 3,38        | 64    | 4      | 3       | 7,31        | (    |

| 5      | 1       | 3,38        | 78    | 3,49        | 62    | 5      | 3       |             | (    |

| 6      | 1       | 3,47        | 76    | 3,61        | 60    | 6      | 3       | 8,25        | (    |

| 7      | 1       | 3,56        | 74    | 3,73        | 58    | 7      |         |             | ,    |

| 8      | 1       | 3,66        | 72    | 3,87        | 56    | 8      | 3       | 9,42        |      |

| 9      | 1       | 3,77        | 70    |             |       | 9      | 3       | 10,17       | 2    |

| 10     | 1       | 3,89        | 68    |             |       | 10     |         | 11,02       | 2    |

| 0      | 2       | 4,00        | 66    | 4,01        | 54    |        |         |             |      |

| 1      | 2       | 4,13        | 64    | 4,15        | 52    |        |         |             |      |

| 2      | 2       | 4,25        | 62    | 4,31        | 50    |        |         |             |      |

| 3      | 2       | 4,41        | 60    | 4,5         | 48    |        |         |             |      |

| 4      | 2       | 4,56        | 58    | 4,69        | 46    |        |         |             |      |

| 5      |         | 4,72        | 56    | 4,9         | 44    |        |         |             |      |

| 6      | 2       | 4,88        | 54    | 5,13        | 42    |        |         |             |      |

| 7      | 2       | 5,06        | 52    | 5,39        | 40    |        |         |             |      |

| 8      | 2       | 5,28        | 50    | 5,7         | 38    |        |         |             |      |

| 9      |         | 5,50        | 48    |             |       |        |         |             |      |

| 10     | 2       | 5,75        | 46    |             |       |        |         |             |      |

Table 4-8 Number of stored lines per field dependent on VSHRNK

# 4.6.2 Horizontal And Vertical Fine Positioning

All picture sizes are pre-centered inside the frame. In addition, if necessary the vertical and horizontal acquisition area can be shifted by **VFP** for vertical and **HFP** for horizontal direction.

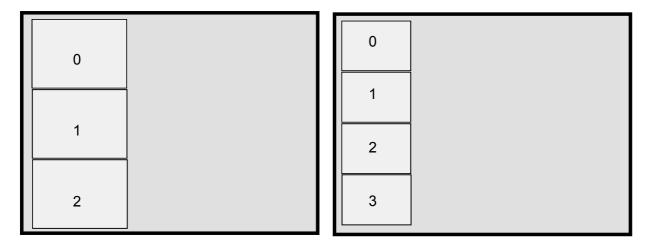

## 4.6.3 Multi Display Mode

SDA 9488X and SDA 9588X offer the feature to display a sub-picture more than once. The picture size and arrangement depends on the display mode (**DISPMOD**) and not on **SIZEVER**. Hence variable scaling is not possible in these modes.

| Display | DISP | MOD | Size                                     | Picture                         | Pixel          | Lir           | nes           |

|---------|------|-----|------------------------------------------|---------------------------------|----------------|---------------|---------------|

| Mode    | D1   | D0  |                                          | configuration                   |                | 625           | 525           |

| 1       | 0    | 0   | SIZEHOR/<br>SIZEVER<br>HSRHNK/<br>VSHRNK | single PIP mode,                | 216<br>-<br>60 | 88<br>-<br>24 | 72<br>-<br>20 |

| 2       | 0    | 1   | 3 X1/9                                   | one upon another (same content) | 216            | 264           | 216           |

| 3       | 1    | 0   | 4 X 1/16                                 | one upon another (same content) | 156            | 264           | 216           |

## Table 4-9 Multi-display modes

The display modes are shown in the appendix. The sizes of the partial pictures are listed in table 4-9.

# 4.7 Display Control

The on-chip memory capacity is 512 kbits. Provided that the same standard (50 or 60 Hz) video sources are applied to inset and parent channel, jointline-free frame mode display is possible. This means that every incoming field is processed and displayed by the SDA 9488X/SDA 9588X processor. The result is a high vertical and time resolution. For this purpose the standard is analyzed internally and frame mode display is blocked automatically, if the described restrictions are not fulfilled. Then only every second incoming field is shown (field mode). Field mode normally shows jointlines. This is caused by an update of the memory during read out. The result is that one part of the picture contains new picture information and the other part contains one earlier written field. The switching from or to frame mode is free of artifacts.

Activation of frame-mode display is blocked automatically if at least one of the following conditions is not fulfilled:

- Inset and parent channel have the same field repetition frequency. This means that frame mode is possible only for 50Hz inset and parent sources or 60Hz inset and parent sources.

- Interlace signal is detected for inset and parent channel. For progressive scan or (S)VGA display therefore only field mode is possible. For some VCRs in trick mode, often no interlace is detected also.

- The number of lines is within a predefined range for inset (FMACTI) or parent (FMACTP) channel (assuming standard signals according to ITU)

| FMACTP | parent<br>standard | number of<br>lines per field | FMACTI | inset<br>standard | number of<br>lines per field |

|--------|--------------------|------------------------------|--------|-------------------|------------------------------|

| 0      | 50 Hz              | 310315                       | 0      | 50 Hz             | 310315                       |

| 1      | 50 Hz              | 290325                       | 1      | 50 Hz             | 290325                       |

| 0      | 60 Hz              | 260265                       | 0      | 60 Hz             | 260265                       |

| 1      | 60 Hz              | 250275                       | 1      | 60 Hz             | 250275                       |

Table 4-10 Required number of lines for frame mode display

The system may be forced to field mode by means of **FIESEL**. Either first or second field is selectable. 'One of both' takes every second field independent of the field number. This is meant for sources generating only one field (e.g. video-games).

For progressive scan conversion systems and HDTV / (S)VGA displays a line doubling mode is available (**PROGEN**). Every line of the inset picture is read twice.

Memory writing is stopped by **FREEZE** bit. The field stored in the memory is then continuously read. As the picture decimation is done before storing, the picture size of a frozen picture can not be changed.

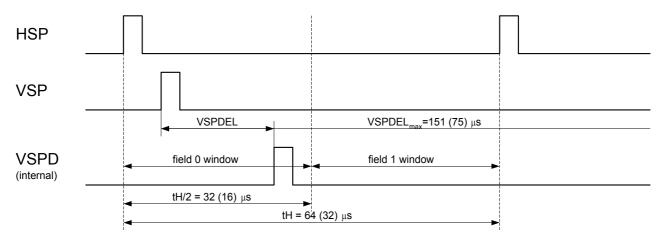

Depending on the phase between inset and parent signals a correction of the display raster for the read out data is performed. Synchronization of memory reading with the parent channel is achieved by processing the parent horizontal and vertical synchronization signals. Horizontal and vertical pulses may be provided. The signals are fed to the IC at pin HSP for horizontal synchronization and pin VSP for vertical synchronization. **HSPINV** or **VSPINV** respectively allow an inversion of the expected signal polarity.

values in brackets () apply for 100Hz systems

Figure 4-7 Field detection and phase adjustment of vertical pulse (VSP)

As the external VSP and HSP signals may come from different devices with different delay paths, the phase between V-sync and H-sync is adjustable (VSPDEL). An incorrect setting of VSPDEL may result in wrong or unreliable field detection of parent channel.

Normally a noise reduction of the incoming parent vertical pulse is performed. With this function missing vertical pulses are compensated. The circuit works for 50/60 Hz applications as well as progressive and 100/120Hz application. (S)VGA signals are supposed to be very stable and therefore not supported by the noise suppression. By means of **VSPNSRQ**, vertical noise suppression is switched off.

A great variety of combinations of inset and parent frequencies are possible. The following table shows some constellations:

| Inset<br>Frequency <sup>1)</sup> | Parent<br>Frequency <sup>1)</sup><br>(HSP/VSP) | frame<br>mode | correct aspect<br>ratio<br>(single pip) | correct aspect<br>ratio<br>(multi display) | vertical<br>noise<br>suppression<br>selectable |

|----------------------------------|------------------------------------------------|---------------|-----------------------------------------|--------------------------------------------|------------------------------------------------|

| 50                               | 50i                                            |               |                                         |                                            |                                                |

| 50                               | 60i                                            |               |                                         |                                            |                                                |

| 60                               | 50i                                            |               |                                         |                                            |                                                |

| 60                               | 60i                                            |               |                                         |                                            |                                                |

| 50                               | 50p                                            |               |                                         |                                            |                                                |

| 50                               | 60p                                            |               |                                         |                                            |                                                |

| 60                               | 50p                                            |               |                                         |                                            |                                                |

| 60                               | 60p                                            |               |                                         |                                            |                                                |

| 50                               | 100i                                           |               |                                         |                                            |                                                |

| 50                               | 120i                                           |               |                                         |                                            |                                                |

| 60                               | 100i                                           |               |                                         |                                            |                                                |

| 60                               | 120i                                           |               |                                         |                                            |                                                |

| 50                               | (S)VGA                                         |               |                                         | 2)                                         |                                                |

| 60                               | (S)VGA                                         |               |                                         | 2)                                         |                                                |

<sup>1)</sup> standard signals supposed

Table 4-11

Available Features with varying inset and parent standards

<sup>&</sup>lt;sup>2)</sup> valid for some parent frequencies. Please refer to **Chapter 4.7.1**

# 4.7.1 Mixed Standard Applications And (S)VGA Support

| remark<br>(N <sub>apel</sub> X N <sub>aline</sub> @ f <sub>V</sub> ) | f <sub>H</sub><br>(kHz) | Τ <sub>Η</sub><br>(μ <b>s</b> ) | T <sub>Hact</sub> (<br>μs) | lines/<br>active | f <sub>dot</sub><br>(MHz) | scan             | correct<br>aspect<br>ratio |

|----------------------------------------------------------------------|-------------------------|---------------------------------|----------------------------|------------------|---------------------------|------------------|----------------------------|

| 720X576@50Hz<br>(TV)                                                 | 15.6                    | 64.0                            | 52.0                       | 625/<br>576      | 13.5                      | interlace        |                            |

| 702X488@60Hz<br>(TV)                                                 | 15.7                    | 63.6                            | 52.7                       | 525/<br>488      | 13.5                      | interlace        |                            |

| 720X576@100Hz<br>(TV 100 Hz)                                         | 31.2                    | 32.0                            | 26.0                       | 625/<br>576      | 27                        | interlace        |                            |

| 702X488@120Hz<br>(TV 120 Hz)                                         | 31.2                    | 31.8                            | 26.4                       | 525/<br>488      | 27                        | interlace        |                            |

| 720X576@50Hz<br>(TV progressive)                                     | 31.2                    | 32.0                            | 26.0                       | 625/<br>576      | 27                        | prog-<br>ressive |                            |

| 702X488@60Hz<br>(TV progressive)                                     | 31.2                    | 31.8                            | 26.4                       | 525/<br>488      | 27                        | prog-<br>ressive |                            |

| 640X480@60Hz<br>(VGA)                                                | 31.5                    | 31.8                            | 25.4                       | 525/<br>480      | 25.2                      | prog-<br>ressive |                            |

| 640X480@72Hz<br>(VGA)                                                | 37.9                    | 26.4                            | 20.3                       | 520/<br>480      | 31.5                      | prog-<br>ressive |                            |

| 640X480@75Hz<br>(VGA)                                                | 37.5                    | 26.7                            | 20.3                       | 500/<br>480      | 31.5                      | prog-<br>ressive |                            |

| 800X600@56Hz<br>(SVGA)                                               | 35.2                    | 28.4                            | 22.2                       | 625/<br>600      | 36.0                      | prog-<br>ressive |                            |

| 800X600@60Hz<br>(SVGA)                                               | 37.9                    | 26.4                            | 20.0                       | 625/<br>600      | 40.0                      | prog-<br>ressive |                            |

| 800X600@72Hz<br>(SVGA)                                               | 48.1                    | 20.8                            | 16.0                       | 666/<br>600      | 50.0                      | prog-<br>ressive |                            |

| 800X600@75Hz<br>(SVGA)                                               | 46.9                    | 21.3                            | 16.2                       | 625/<br>600      | 49.5                      | prog-<br>ressive |                            |

| 800X600@85Hz<br>(SVGA)                                               | 53.7                    | 18.6                            | 14.2                       | 631/<br>600      | 56.3                      | prog-<br>ressive |                            |

| 1024X768@43Hz<br>(SVGA)                                              | 35.5                    | 28.2                            | 22.8                       | 817/<br>768      | 44.9                      | interlace        |                            |

Table 4-12 Examples of supported parent signals

The SDA 9488X resp. SDA 9588X allow multiple scan rates for the use in desktop video applications, VGA compatible or 100Hz TV sets. All features are provided in 'normal' operating modes at auto detected 50Hz and 60 Hz parent and inset standards.  $2f_H$  modes (100/120Hz and progressive) are supported by line frequency- and pixel clock doubling and are not detected automatically. Even on a 16:9 picture tube correct aspect ratio can be displayed by selecting the approbiate parent clock. The video synthesizer generates also a special pixel clock for VGA display (see chapter 5.5.9 for details). As (S)VGA consists of a variety of scan rates the correct aspect ratio is not adjustable for all modes with the parent clock (**HZOOM**) because of the limited count of frequencies. For single PIP only, correct aspect ratio is maintained by the vertical and horizontal scaler (**HSHRINK** and **VSHRINK**).

It is possible to display (S)VGA sources for parent display, as long as the horizontal frequency is lower than 40 kHz and the signal does not contain more than 1023 lines. For progressive scan mode, **PROGEN** must be set. Additionally *field-mode* should be forced to prevent unallowed *frame-mode* displaying (**FIESEL**). As the (S)VGA normally does not fit to the display raster generated in the vertical noise suppression, **VSPNSRQ** should be disabled. (S)VGA signals for inset channel are not supported.

| PROGEN | READD | Expected input signal                    |

|--------|-------|------------------------------------------|

| 0      | 0     | 50 or 60 Hz signal interlace             |

| 0      | 1     | 100 or 120 Hz signals interlace          |

| 1      | 0     | (reserved)                               |

| 1      | 1     | 50 or 60 Hz or (S)VGA signal progressive |

Table 4-13 Selection of display field repetition

## 4.7.2 Display standard

For a single-PiP, the number of displayed lines depends on the selected picture size and on the signal standard. For multi picture display, the number of displayed lines depends on the selected picture size and on the signal standard of the parent signal. Additionally, a standard can be forced by **DISPSTD**.

| DISF | STD | DISPMOD | Display Standard                                        |

|------|-----|---------|---------------------------------------------------------|

| D1   | D0  |         |                                                         |

| 0    | 0   | 0       | PIP depends on detected inset standard (single pip)     |

| 0    | 0   | >0      | PIP depends on detected parent standard (multi display) |

| 0    | 1   | Х       | PIP display is always in 625 lines mode                 |

| 1    | 0   | Х       | PIP display is always in 525 lines mode                 |

| 1    | 1   | Х       | freeze last detected display standard and size          |

#### Table 4-14 Display standard selection

If a 625 lines picture is shown with a 525 lines parent signal, some lines are missing on top and bottom of picture. If a 525 lines picture is shown with a 625 lines display standard, missing lines at top and bottom are filled with background color.

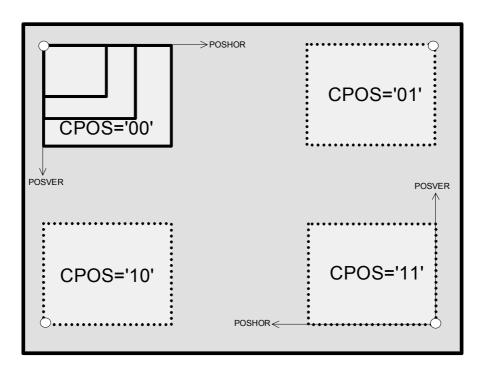

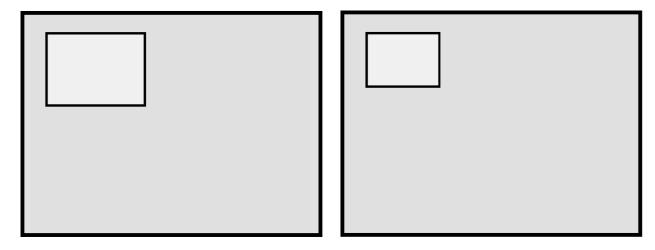

## 4.7.3 Picture Positioning

The display position of the inset picture is programmable to the 4 corners of the parent picture (CPOS). From there PIP can be moved to the middle of the TV Picture with POSHOR and POSVER. The corner positions can be centered coarsely on the screen with POSOFH and POSOFV. Depending on coarse position, one PIP corner remains stable when changing the picture size.

| СР | os | Coarse      | Reference     | increasing | increasing |  |

|----|----|-------------|---------------|------------|------------|--|

| D1 | D0 | Position    | corner of PiP | POSVER     | POSHOR     |  |

| 0  | 0  | upper left  | upper left    | down       | right      |  |

| 0  | 1  | upper right | upper right   | down       | left       |  |

| 1  | 0  | lower left  | lower left    | up         | right      |  |

| 1  | 1  | lower right | lower right   | up         | left       |  |

#### **Table 4-15 Coarse Positioning**

Starting at every coarse position, the picture is movable to 256 horizontal locations (4 pixel increments) and 256 vertical locations (2 line increments). The pixel width on the screen depends on the selected **HZOOM** factor. Even POP-positions (Picture Outside Picture) in 16:9 applications are possible.

Figure 4-8 Coarse Positioning

# 4.8 Output Signal Processing

#### 4.8.1 Luminance Peaking

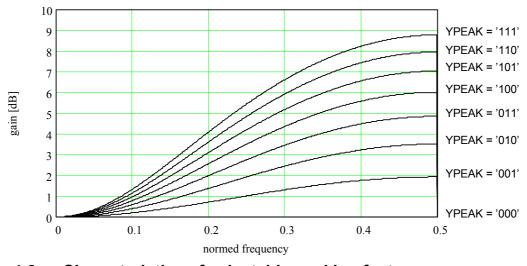

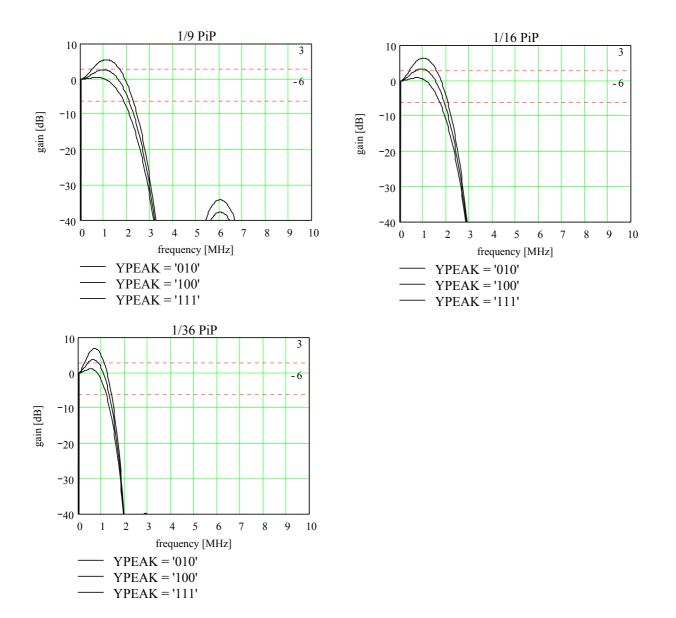

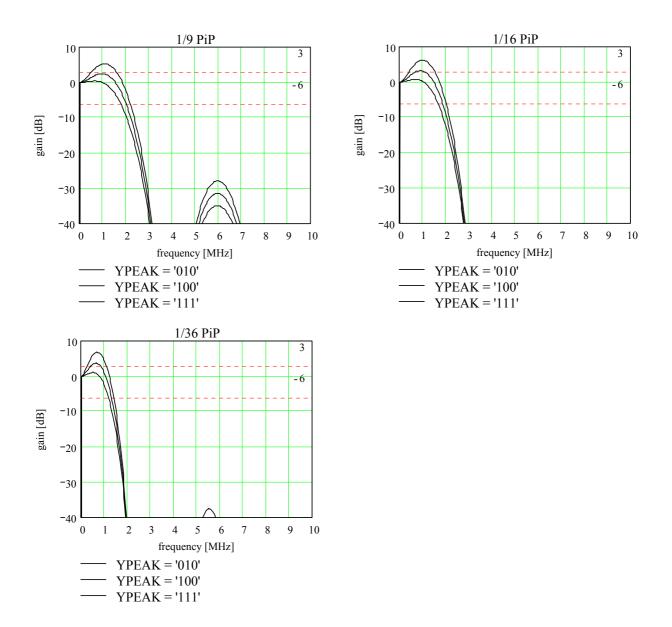

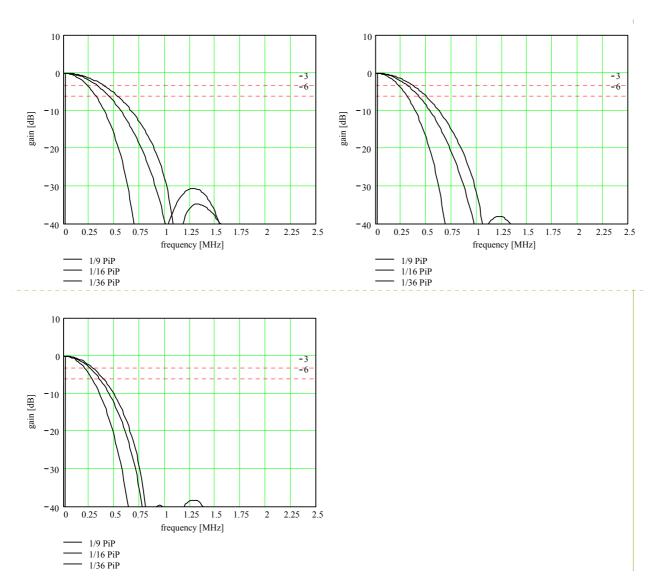

To improve picture sharpness, a peaking filter which amplifies higher frequencies of the input signal is implemented. The amount of peaking can be varied in seven steps by **YPEAK**. The setting '000' switches off the peaking. The value '011' is recommended. This provides a good compromise between sharpness impression and annoying aliasing. The characteristic for all possible settings is shown in fig. (4-9)

Figure 4-9 Characteristics of selectable peaking factors

Coring should be switched on by **YCOR** to reduce noise, which is also amplified when peaking is enabled. As the coring stage is in front of the peaking filter, 1 LSB noise will not be peaked.

#### 4.8.2 RGB Matrix

The chip contains three different matrices, one suited for EBU standards, one suited for NTSC-Japan and one suited for NTSC-USA, which are selected via **MAT**. The signal **OUTFOR** switches between YUV output or RGB output. The signal **UVPOLAR** inverts the U and V channels and results in Y-U-V output. The standard magnitudes and angles of the color-difference signals in the UV-plane are defined as follows:

| M  | <b>Δ</b> Τ | M     | agnitude | es    | Angles |       |       | Standard     |

|----|------------|-------|----------|-------|--------|-------|-------|--------------|

| D1 | D0         | (B-Y) | (R-Y)    | (G-Y) | (B-Y)  | (R-Y) | (G-Y) |              |

| 0  | 0          | 2.028 | 1.14     | 0.7   | 0      | 90    | 236   | EBU          |

| 0  | 1          | 2.028 | 1.582    | 0.608 | 0      | 95    | 240   | NTSC (Japan) |

| 1  | 0          | 2.028 | 2.028    | 0.608 | 0      | 105   | 250   | NTSC (USA)   |

| 1  | 1          |       |          |       |        |       |       | (reserved)   |

Table 4-16 RGB matrices characteristics

The color saturation can be adjusted with **SATADJ** register in 16 steps between 0 and 1.875. Values above 1.0 may clip the chrominance signals.

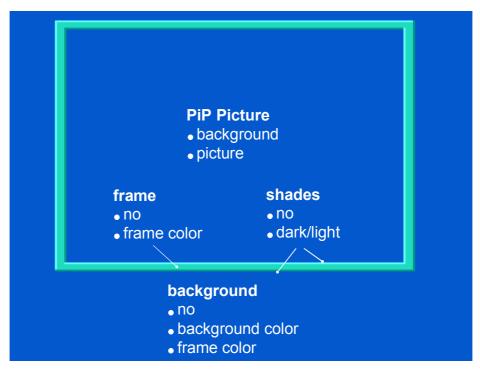

# 4.8.3 Framing And Colored Background

Figure 4-10 Normal frame and 3D frame

With **FRSEL** a colored frame is added to the inset picture. The chip can display two different types of frames, one simple monochrome frame and a more sophisticated frame giving a three dimensional impression.

The frame elements are always placed outside the inset picture, except for the inner shade of three dimensional frame or inner frame in multipip-mode. There is no shift of the inset picture position if the inset frame width is modified.

4096 frame colors are programmable by **FRY**, **FRU**, and **FRV**, 4 bits for each component. Horizontal and vertical width of the frame are programmable independently by **FRWIDH** and **FRWIDHV**. If desired, frame color is displayed over the whole PIP size or whole picture size of the main channel when **PIPBG** is set accordingly.

Figure 4-11 Selectable picture configurations

64 background colors are programmable by **BGY**, **BGU**, **BGV**, 2 bits for each component. Alternatively **BGFRC** sets the background to frame color.

#### 4.8.4 16:9 Inset Picture Support

To remove dark stripes at 16:9 inset pictures the vertical display area is reducable with **VPSRED**. The number of omitted lines depends on the vertical decimation factor.

| vertical<br>decimation<br>factor | displayed<br>lines (50Hz) | displayed<br>lines (50Hz)<br>with reduction | displayed<br>lines (60Hz) | displayed<br>lines (60Hz)<br>with reduction |  |

|----------------------------------|---------------------------|---------------------------------------------|---------------------------|---------------------------------------------|--|

| 1                                | 264                       | 214                                         | 216                       | 175                                         |  |

|                                  |                           |                                             |                           |                                             |  |

| 6                                | 44                        | 35                                          | 36                        | 29                                          |  |

Figure 4-12 Number of lines without and with reduction of vertical picture size

Figure 4-13 16:9 inset picture without and with reduction of vertical picture size

#### 4.8.5 Parent Clock Generation

The phase of the output signals is locked to the rising edge of the horizontal sync pulse. The frequency varies in a certain range to ensure correct aspect ratio for 16:9 applications depending on **HZOOM**. The horizontal and vertical scaling can be used for all display frequencies.

| display | inset             | desired    | required            | value | value of HZOOM |    |  |  |

|---------|-------------------|------------|---------------------|-------|----------------|----|--|--|

| format  | picture<br>format | PiP format | parent<br>frequency | D2    | D1             | D0 |  |  |

| 4:3     | 4:3               | 4:3        | 27                  | 0     | 0              | 0  |  |  |

| 4:3     | 4:3               | 16:9       | 20.25               | 0     | 0              | 1  |  |  |

| 16:9    | 4:3               | 4:3        | 36                  | 0     | 1              | 0  |  |  |

| 16:9    | 16:9              | 16:9       | 36                  | 0     | 1              | 0  |  |  |

Table 4-17 Format conversion using HZOOM

For variations of parental horizontal frequency (e.g. VCR), a digital correction of the position is useful to stabilize the picture (**POSCOR**). This circuit detects a varying parental line frequency and moves the picture to the place, where it would have been without this frequency deviation. The calculation is done once a field.

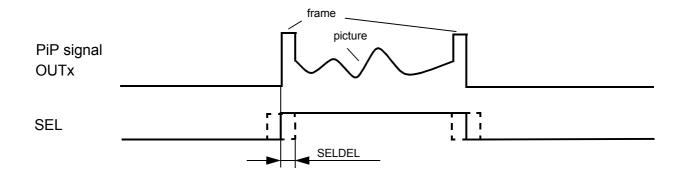

## 4.8.6 Select Signal

For controlling an external RGB or YUV switch a select signal is supplied. The delay of this signal is programmable for adaptation to different external output signal processing devices (**SELDEL**). **SELDOWN** sets this output to tristate (high-resistance).

Figure 4-14 Select timing

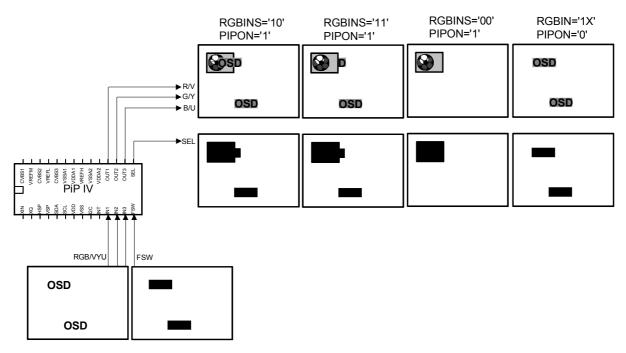

#### 4.9 DA-Conversion And RGB / YUV Switch

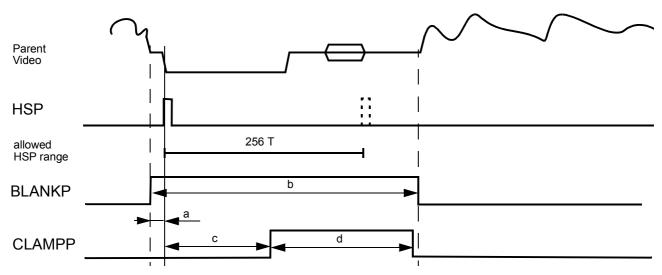

The SDA 9588X/SDA 9488X include three 7bit DA-converters. Brightness (**BRTADJ**), Contrast (**CON**) and overall amplitude (**PKLR**, **PKLG**, **PKLB**) of the output signal are adjustable. External RGB or YUV signals can be connected to the inputs IN1...3. By forcing the FSW input to high-level these signals are switched to the outputs OUT1...3 while the internal signals are switched off. The FSW input signal is passed through to the SEL output. The setting of **RGBINS** determines wether an RGB insertion is possible and which source, the external picture or the PiP, gets priority.

Figure 4-15 Visualization of RGB/YUV insertion

The external RGB or YUV signals are each clamped to the reference levels of the DACs to force uniform black levels in each channel. The clamping needs careful adjustment especially for VGA applications. The position and the length of the blanking pulse as well as the clamping pulse are adjustable (**CLPPOS, CLPLEN**). If **READD** is set to '1' (100Hz mode), all pulses are shortened by one half. **HZOOM** influences the adjustment range of the clamping and blanking pulse because of the modified clock frequency, but the pulse length is kept nearly constant.

Figure 4-16 PIP horizontal blanking timing

| READD | C  | LPDE | L  | CLP | LEN | <b>a</b> (μ <b>s</b> ) | <b>b</b> (μ <b>s</b> ) | <b>c</b> (μ <b>s</b> ) | <b>d</b> (μ <b>s</b> ) |

|-------|----|------|----|-----|-----|------------------------|------------------------|------------------------|------------------------|

|       | D2 | D1   | D0 | D1  | D0  | Blanking<br>Start      | Blanking<br>Duration   | Clamping<br>Start      | Clamping<br>Duration   |

| 0     | 0  | 0    | 0  | 0   | 0   | -1.5                   | 10.5                   | 3                      | 5                      |

| 0     | 1  | 1    | 1  | 0   | 0   | -11                    | 10.5                   | -6.4                   | 5                      |

| 0     | 0  | 0    | 0  | 0   | 1   | -1.5                   | 7.9                    | 2.2                    | 3.8                    |

| 0     | 1  | 1    | 1  | 0   | 1   | -11.0                  | 7.9                    | -7.3                   | 3.8                    |

| 1     | 0  | 0    | 0  | 0   | 0   | -0.8                   | 5.3                    | 1.5                    | 2.5                    |

| 1     | 1  | 1    | 1  | 0   | 0   | -5.5                   | 5.3                    | -3.2                   | 2.5                    |

| 1     | 0  | 0    | 0  | 0   | 1   | -0.8                   | 4                      | 1.1                    | 1.9                    |

| 1     | 1  | 1    | 1  | 0   | 1   | -5.5                   | 4                      | -3.6                   | 1.9                    |

Table 4-18 PIP horizontal blanking timing

## 4.9.1 Contrast, Brightness and Peak Level Adjustment

The peak level adjustment modifies the magnitude of each channel separately. It should be used to adapt once the signal levels to the following stage. The contrast adjustment influences all three channels and allows a further increase of 30% of the peak level magnitude. The effect of the brightness adjustment depends on the selected output mode (RGB/YUV). In YUV mode it changes the offset of the OUT2 (Y) signal only while in RGB mode it changes the offset of all three channels at the same time. The brightness increase is up to 20%.

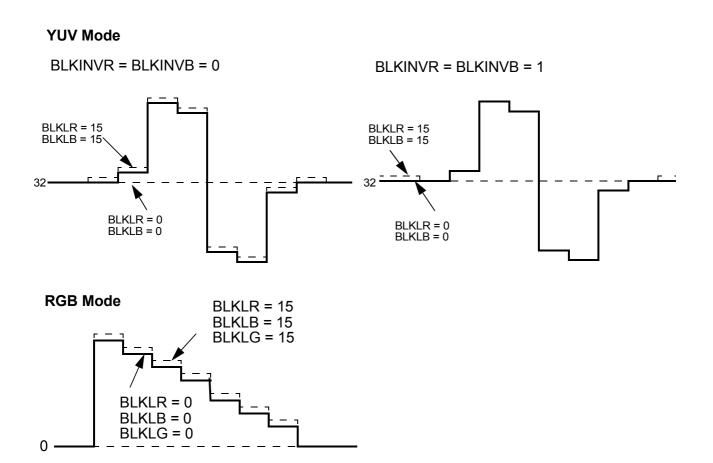

# 4.9.2 Pedestal Level Adjustment

The pedestal level adjustment controlled by I<sup>2</sup>C signals **BLKLR**, **BLKLG**, **BLKLB** enables the correction of small offset errors, possibly appearing at the successive blanking stage of RGB processor. This adjustment has an effect on the setup level during the active line interval of each channel like the brightness adjustment but has an enhanced resolution of 0.5 LSB. The maximum possible offset amounts to 7.5 LSBs. In YUV mode (**OUTFOR** = '1') the action depends on the setting of **BLKINVR** and **BLKINVB**. If **BLKINVR** (**BLKINVB**) is active the offset applies to the blank level of the **RV** (**BU**) channel during the clamping interval for shifting the setup level to the negative direction. In RGB mode (**OUTFOR** = '0') **BLKINVR** and **BLKINVB** have no effect.

Figure 4-17 Pedestal level adjustment

#### 4.10 Data Slicer

Depending on **SERVICE**, Closed Caption data ('Line 21') or WSS (Widescreen signalling) is sliced by the digital data slicer and can be read out from I<sup>2</sup>C interface. The line number of the sliced data is selectable with **SELLNR**. Therefore WSS and CC can be processed in different regions (e.g. CC with PAL M). The Closed Caption data is assumed to conform with the ITU standards EIA-608 and EIA-744-A. WSS data is assumed to conform with ETS 300 294 (2nd edition, May 1996).

#### 4.10.1 Closed Caption

The closed caption data stream contains different data services. In field 1 (line 21) the captions CC1 and CC2 and the text pages T1 and T2 are transmitted whereas in field 2 (line 284) caption CC3, CC4, text T3, T4 and the XDS data are transmitted. For more information please refer to the above mentioned standards.

Raw CC as well as prefiltered data is provided alternatively. With the built-in programmable XDS-Filter (XDSCLS), the program-rating information ('V-chip') as well

as others can be filtered out. The XDS filter reduce traffic on the I<sup>2</sup>C bus and save calculation power of the main controller. If no class filter is selected, all incoming data (both fields) is sliced and provided by the I<sup>2</sup>C interface. When one or more class filters are chosen, only data in field 2 is sliced. Any combination of class filters is allowed. Each 'CLASS' is divided into 'TYPES' which can be sorted out by the XDS-secondary filter (**XDSTPE**). Any combination of type filter is allowed. Some type filter require an appropriate class filter.

## 4.10.2 Widescreen Signalling (WSS)

In WSS mode (**SERVICE**='1') no filtering is possible. All sliced data is passed to the output registers. In this case **XDSTPE** selects the field number of the data to be sliced. In Europe WSS carries for instance information about aspect ratio and movie mode.

#### 4.10.3 Indication Of New Data

The sliced and possibly filtered data is available in **DATAA** and **DATAB**. The corresponding status bits are **DATAV** and **SLFIELD**. When new data were received, **DATAV** becomes '1' and the controller must read **DATAA**, **DATAB** and the status information. After both data bytes were read **DATAV** becomes '0' until new data arrives. It must be ensured that the data polling is activated once per field (16.7 or 20 ms) or every second field (33.3 or 40 ms), depending on the slicer configuration and inset field frequency. The field number of the data in **DATAA** and **DATAB** can be found in **SLFIELD**. If one or more XDS-class filter are activated, **SLFIELD** contains always '1'.

Additionally pin 10 (INT) may flag that new data is received. Default this pin is in tri-state mode to be compatible with Micronas' SDA9388X/9389X PIP devices. It can also be configured by **IRQCON** to output a single short pulse when new data is available or behave equal to **DATAV**. In the last case the output remains active until the two data registers **DATAA/DATAB** are read. Both modes are useful to avoid continuos polling of the I2C bus. The micro-controller initiates I2C transfers only when required.

```

while (1) {

i2c_read pip4_adr, status_reg_adr, status

if (status & data_valid_mask) {

i2c_read_inc pip4_adr, dataa_reg_adr, dataa, datab, status

process_data dataa, datab, status

}

}

```

Figure 4-18 Example in pseudo-code for reading the data

#### 4.10.4 Violence Protection

The rating information is sent in the program rating packet of the current (sometimes future) class in the XDS data stream. If only this information is desired the corresponding XDS filter (class 01h, type 05h) should be used to suppress other data. The class/packet bytes (0105h) precede the 2 bytes rating information. Each sequence is closed by the end-of-packet byte (0fh) and a checksum. This checksum complements the byte truncated sum of all bytes to 00h. Except comparison of the received rating with the adjusted user rating threshold the micro-controller should check the parity of each byte and validate the checksum to avoid miss-interpretation of wrong received data.

The SDA 9488X/SDA 9588X offer some alternatives to blocking the PIP channel completely by switching it off (fig. (4-19)).

Figure 4-19 Possibilities of PiP blocking

The Mosaic mode (**MOSAIC**) hides details of the picture by reduced sharpness and increased aliasing. The picture looks scrambled and is less perceptible.

## **Application Examples**

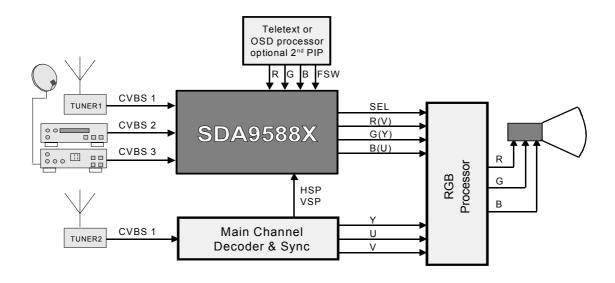

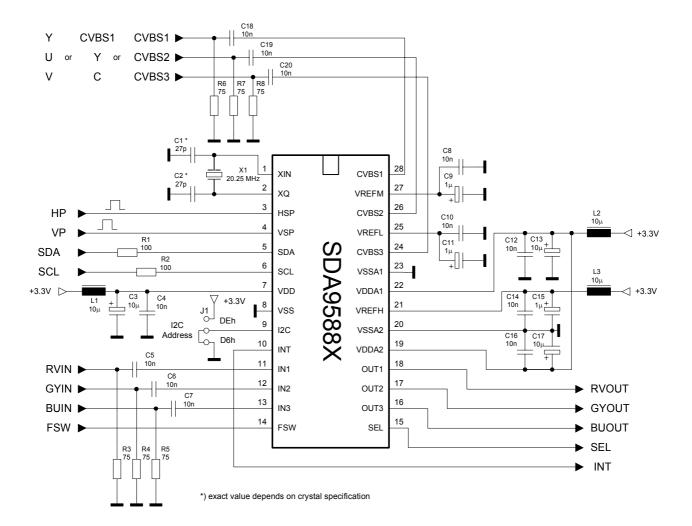

# 5 Application Examples

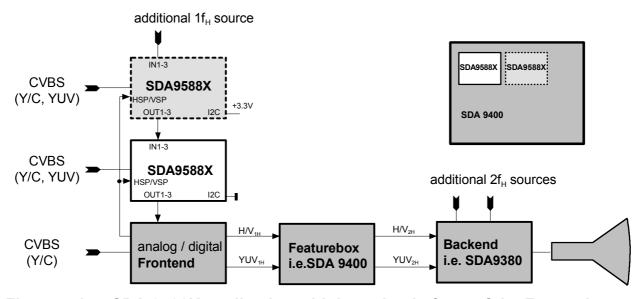

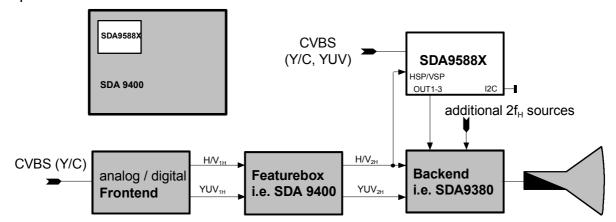

The following two figures show 100/120Hz applications with the Micronas Featurebox SDA 9400/01. As the chip supports two I2C addresses and owns a RGB switch dual-PiP applications are easy to implement. The arrangement for best possible performance is shown in the fig. (5-1).

Figure 5-1 SDA 9588X application with insertion in front of the Featurebox

The output of two 'OCTOPUS' are connected to the YUV (or RGB) input of the video processor of the main channel. Due to the 4:2:2 processing within the SDA 9400 the inset picture remains brilliant.

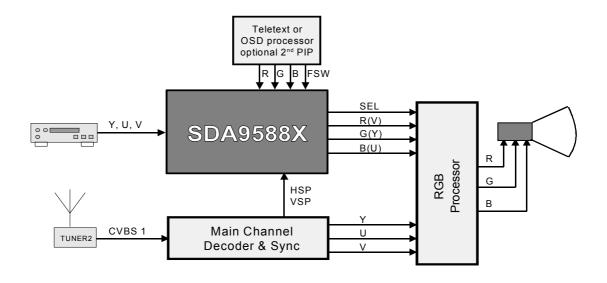

Figure 5-2 SDA 9588X application with insertion behind the featurebox

Connecting of a SDA 9588X directly to the RGB input of the RGB processor is possible as well. One picture is generated from SDA 9588X device, the other one from the featurebox. This cheap implementation preserves the chroma of inset channel at its full bandwidth, although only field mode is possible for PiP picture. The output of an OSD/Text processor may be fed to the RGB switch of the SDA 9588X.

#### 6 I<sup>2</sup>C Bus

#### 6.1 I<sup>2</sup>C Bus Address

| Write Address1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | (D6h) |

|----------------|---|---|---|---|---|---|---|---|-------|

| Read Address1  | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | (D7h) |

#### Table 6-1 Primary Address (pin 9='low-level')

| Write Address2 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | (DEh) |

|----------------|---|---|---|---|---|---|---|---|-------|

| Read Address2  | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | (DFh) |

#### Table 6-2 Secondary Address (pin 9 = 'high-level')

#### 6.2 I<sup>2</sup>C-Bus Format

| WRITE | S | 1101x110 | Α | Subaddress | Α | Data Byte |          | Α | ****        | Α  | Р |

|-------|---|----------|---|------------|---|-----------|----------|---|-------------|----|---|

| READ  | S | 1101x110 | Α | Subaddress | Α | Sr        | 1101x111 | Α | Data Byte n | NA | Р |

S: Start condition / Sr Repeated start condition / A: Acknowledge / P: Stop condition / NA: No Acknowledge

Write operation is possible at registers 00h-21h only, read operation is possible at registers 28, 2Ah-2Ch only. An automatic address increment function is implemented.

6-37

Micronas

# 6.3 I<sup>2</sup>C bus Command Table

| Subadd<br>(Hex) |          | Data Byte |          |         |          |          |          |          |  |

|-----------------|----------|-----------|----------|---------|----------|----------|----------|----------|--|

| (пех)           | D7       | D6        | D5       | D4      | D3       | D2       | D1       | D0       |  |

| 00h             | PIPON    | CPOS1     | CPOS0    | YUVSEL  | READD    | PROGEN   | FIESEL1  | FIESEL0  |  |

| 01h             | POSHOR7  | POSHOR6   | POSHOR5  | POSHOR4 | POSHOR3  | POSHOR2  | POSHOR1  | POSHOR0  |  |

| 02h             | POSVER7  | POSVER6   | POSVER5  | POSVER4 | POSVER3  | POSVER2  | POSVER1  | POSVER0  |  |

| 03h             | VFP3     | VFP2      | VFP1     | VFP0    | HFP3     | HFP2     | HFP1     | HFP0     |  |

| 04h             | DISPSTD1 | DISPSTD0  | FREEZE   | MOSAIC  | SIZEHOR1 | SIZEHOR0 | SIZEVER1 | SIZEVER0 |  |

| 05h             | FPSTD1   | FPSTD0    | PIPBG1   | PIPBG0  | FMACTP   | HZOOM2   | HZOOM1   | HZOOM0   |  |

| 06h             | HSPINV   | VSPINV    | VSPNSRQ  | VSPDEL4 | VSPDEL3  | VSPDEL2  | VSPDEL1  | VSPDEL0  |  |

| 07h             | FRSEL    | INFRM     | VPSRED   | FRWIDH2 | FRWIDH1  | FRWIDH0  | FRWIDV1  | FRWIDV0  |  |

| 08h             | RGBINS1  | RGBINS0   | VERBLK   | SELDOWN | SELDEL3  | SELDEL2  | SELDEL1  | SELDEL0  |  |

| 09h             | POSCOR   | DISPMOD1  | DISPMOD0 | CLPDEL4 | CLPDEL3  | CLPDEL2  | CLPDEL1  | CLPDEL0  |  |

| 0Ah             | AGCRES   | AGCMD1    | AGCMD0   | AGCVAL3 | AGCVAL2  | AGCVAL1  | AGCVAL0  | NOSIGB   |  |

| 0Bh             | CVBSEL1  | CVBSEL0   | CLMPID1  | CLMPID0 | CLMPIST1 | CLMPIST0 | LMOFST1  | LMOFST0  |  |

| 0Ch             | PLLITC1  | PLLITC0   | NSRED1   | NSRED0  | YCDEL3   | YCDEL2   | YCDEL1   | YCDEL0   |  |

| 0Dh             | CSTAND2  | CSTAND1   | CSTAND0  | CSTDEX1 | CSTDEX0  | LOCKSP   | CKILL1   | CKILL0   |  |

| 0Eh             | BGPOS    | SCMIDL0   | DEEMP1   | DEEMP0  | COLON    | ACCFIX   | CHRBW1   | CHRBW0   |  |

| 0Fh             | IFCOMP1  | IFCOMP0   | HUE5     | HUE4    | HUE3     | HUE2     | HUE1     | HUE0     |  |

| 10h             | SATNR    | FMACTI    | CPLLOF   | SCADJ4  | SCADJ3   | SCADJ2   | SCADJ1   | SCADJ0   |  |

| 11h             | CONADJ3  | CONADJ2   | CONADJ1  | CONADJ0 | BLKLR3   | BLKLR2   | BLKLR1   | BLKLR0   |  |

| 12h             | BRTADJ3  | BRTADJ2   | BRTADJ1  | BRTADJ0 | BLKLG3   | BLKLG2   | BLKLG1   | BLKLG0   |  |

| 13h             | TRIOUT   | REFINT    | BLKINVR  | BLKINVB | BLKLB3   | BLKLB2   | BLKLB1   | BLKLB0   |  |

| 14h             | PKLR7    | PKLR6     | PKLR5    | PKLR4   | PKLR3    | PKLR2    | PKLR1    | PKLR0    |  |

| 15h             | PKLG7    | PKLG6     | PKLG5    | PKLG4   | PKLG3    | PKLG2    | PKLG1    | PKLG0    |  |

| 16h             | PKLB7    | PKLB6     | PKLB5    | PKLB4   | PKLB3    | PKLB2    | PKLB1    | PKLB0    |  |

| Subadd<br>(Hex) |            |            |            | Data       | Byte       |            |         |         |

|-----------------|------------|------------|------------|------------|------------|------------|---------|---------|

| (пех)           | D7         | D6         | D5         | D4         | D3         | D2         | D1      | D0      |

| 17h             | MAT1       | MAT0       | BGY1       | BGY0       | FRY3       | FRY2       | FRY1    | FRY0    |

| 18h             | OUTFOR     | UVPOLAR    | BGU1       | BGU0       | FRU3       | FRU2       | FRU1    | FRU0    |

| 19h             | (reserved) | BGFRC      | BGV1       | BGV0       | FRV3       | FRV2       | FRV1    | FRV0    |

| 1Ah             | SATADJ3†   | SATADJ2    | SATADJ1    | SATADJ0†   | YPEAK2     | YPEAK1     | YPEAK0  | YCOR    |

| 1Bh             | XDSCLS4    | XDSCLS3    | XDSCLS2    | XDSCLS1    | XDSCLS0    | XDSTPE2    | XDSTPE1 | XDSTPE0 |

| 1Ch             | UVSEQ      | MPIPBG     | SERVICE    | SELLNR1    | SELLNR0    | IRQCON2    | IRQCON1 | IRQCON0 |

| 1Dh             | (reserved) | (reserved) | (reserved) | (reserved) | (reserved) | PIPBLK     | PALIDL1 | PALIDL0 |

| 1Eh             | POSOFV2    | POSOFV1    | POSOFV0    | POSOFH4    | POSOFH3    | POSOFH2    | POSOFH1 | POSOFH0 |

| 1Fh             | (reserved) | (reserved) | (reserved) | VSHRNK4    | VSHRNK3    | VSHRNK2    | VSHRNK1 | VSHRNK0 |

| 20h             | (reserved) | (reserved) | (reserved) | HSHRNK4    | HSHRNK3    | HSHRNK2    | HSHRNK1 | HSHRNK0 |

| 21h             | (reserved) | (reserved) | (reserved) | (reserved) | (reserved) | (reserved) | CLPLEN1 | CLPLEN0 |

| 28h             | FRMMD      | PIPSTAT    | SYNCST1    | SYNCST0    | CKSTAT     | STDET2     | STDET1  | STDET0  |

| 2Ah             | DATAA7     | DATAA6     | DATAA5     | DATAA4     | DATAA3     | DATAA2     | DATAA1  | DATAA0  |

| 2Bh             | DATAB7     | DATAB6     | DATAB5     | DATAB4     | DATAB3     | DATAB2     | DATAB1  | DATAB0  |

| 2Ch             |            |            | DEVICE1    | DEVICE0    | PRNSTD     | PALID      | DATAV   | SLFIELD |

After power on the grey marked data bits are set to '1', all other to '0'.

# 6.4 I<sup>2</sup>C Bus Command Description

#### Subaddress 00h

| PIPON | PiP on                        |

|-------|-------------------------------|

| D7    | switches the PIP insertion on |

| 0     | PIP insertion off             |

| 1     | PIP insertion on              |

| СР | os | Coarse position                   |

|----|----|-----------------------------------|

| D6 | D5 | coarse positioning of the picture |

| 0  | 0  | upper left position               |

| 0  | 1  | upper right position              |

| 1  | 0  | lower left position               |

| 1  | 1  | lower right position              |

| YUVSEL | YUV Select         |

|--------|--------------------|

| D4     | select YUV mode    |

| 0      | CVBS or Y/C source |

| 1      | YUV source         |

| READD | Read Double Mode                                                                            |

|-------|---------------------------------------------------------------------------------------------|

| D3    | double read frequency for compatibility with systems that use 2fH (e.g.100 Hz, progressive) |

| 0     | PIP display with single read frequency and 2x oversampling                                  |

| 1     | PIP display with double read frequency                                                      |

| PROGEN | Progressive Scan Enable                                  |

|--------|----------------------------------------------------------|

| D2     | for compatibility with progressive scan systems          |

| 0      | each line of PIP is read once (normal operation)         |

| 1      | each line of PIP is read twice (line doubling operation) |

| FIE | SEL | Field Select                    |  |  |  |

|-----|-----|---------------------------------|--|--|--|

| D1  | D0  | set field or frame display mode |  |  |  |