# Audio Processor Subsystem

SLAS141 November 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

# Contents

| Section                                                  | Title                                                                                                                                                                                                                                                                                                              | Page                            |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| <b>1</b> Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | Deduction         Features         Applications         Functional Block Diagram         Terminal Assignments         Ordering Information         Terminal Functions                                                                                                                                              | 1–1<br>1–2<br>1–3<br>1–4<br>1–4 |

| <b>2 Fun</b><br>2.1                                      | ctional Description         Audio Input Ports                                                                                                                                                                                                                                                                      | 2–2<br>2–2<br>2–5<br>2–6<br>2–7 |

| 2.2                                                      | Analog Audio Outputs                                                                                                                                                                                                                                                                                               | 2–7<br>2–8                      |

| 2.3                                                      | Volume/Balance/Mute Control                                                                                                                                                                                                                                                                                        |                                 |

| 2.4                                                      | Sigma-Delta DAC                                                                                                                                                                                                                                                                                                    | 2–9<br>2–9                      |

| 2.5                                                      | Serial Control Port         2.5.1       Serial Control Port Description         2.5.2       Serial Control Command Format         2.5.3       Power-Down/Reset                                                                                                                                                     | 2–9<br>2–9<br>2–10<br>2–11      |

| 2.6                                                      | Software Interface                                                                                                                                                                                                                                                                                                 | 2–11                            |

| 3 Spe<br>3.1<br>3.2                                      | cificationsAbsolute maximum ratings over operating free-air temperature rangeRecommended Operating Conditions3.2.1 Static Digital Specifications, T <sub>A</sub> = 25°C, AV <sub>DD</sub> = DV <sub>DD</sub> = 5 V + 5%3.2.2 Power Supplies, T <sub>A</sub> = 25°C, AV <sub>DD</sub> = DV <sub>DD</sub> = 5 V + 5% | 3–1<br>3–1<br>3–1               |

# **Contents (Continued)**

| Section                  | Title                                                                                                  | Page    |

|--------------------------|--------------------------------------------------------------------------------------------------------|---------|

| 3.3 Electrical Characte  | eristics                                                                                               | 3–2     |

|                          | io Channel Performance, T <sub>A</sub> = 25°C,                                                         |         |

|                          | DD = 5 V + 5%                                                                                          | 3–2     |

|                          | ntrol and Output Drivers Performance, $T_A = 25^{\circ}C$ ,                                            |         |

|                          | $DD = 5 V + 5\% \dots$                                                                                 | 3–3     |

|                          | ecoder Performance, $T_A = 25^{\circ}C$ ,                                                              | 2.2     |

|                          | $_{DD}$ = 5 V + 5%, f <sub>s</sub> = 32 kHz<br><i>I</i> ultiplexer Performance, T <sub>A</sub> = 25°C, | ə-ə     |

|                          | $= 5 \text{ V} + 5\% \dots = 5 \text{ V} + 5\%$                                                        | 3_4     |

|                          | Channel Performance, $T_A = 25^{\circ}C$ ,                                                             |         |

|                          | $D_{DD} = 5 \text{ V} + 5\%, \text{ f}_{s} = 48 \text{ kHz}$                                           |         |

|                          | blation Filter, $T_A = 25^{\circ}C$ ,                                                                  |         |

|                          | <sub>DD</sub> = 5 V + 5%, f <sub>s</sub> = 48 kHz                                                      | 3–4     |

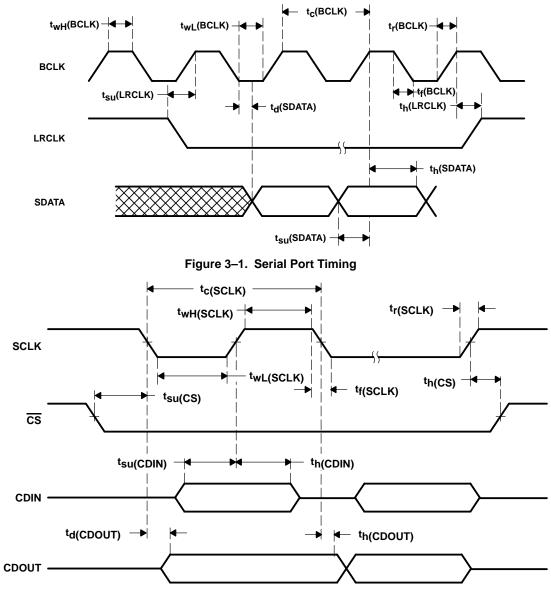

| 3.4 Timing Requirement   | nts, T <sub>A</sub> = 25°C, AV <sub>DD</sub> = DV <sub>DD</sub> = 5 V + 5%, f <sub>s</sub> = 48        | kHz 3–5 |

|                          | Data Port                                                                                              |         |

| 3.4.2 Serial Contr       | fol Interface, $T_A = 25^{\circ}C$ , $AV_{DD} = DV_{DD} = 5 V + 5\%$                                   | b, 3–5  |

| 4 Application Informatio | n                                                                                                      | 4–1     |

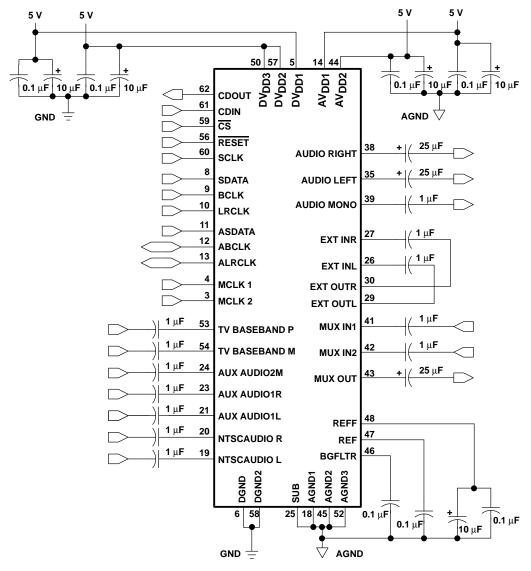

| 4.1 Schematic            |                                                                                                        | 4–3     |

| Appendix A: Register Set |                                                                                                        | A–1     |

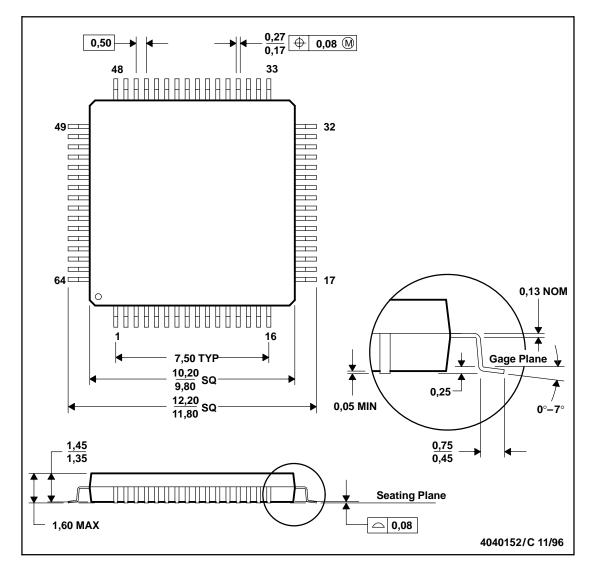

| Appendix B: Mechanical D | Pata                                                                                                   | В–1     |

# **List of Illustrations**

| Figure | Title                                                     | Page |

|--------|-----------------------------------------------------------|------|

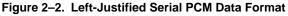

| 2–1    | Philips I <sup>2</sup> S Protocol Serial PCM Data Format  | 2–3  |

| 2–2    | Left-Justified Serial PCM Data Format                     | 2–3  |

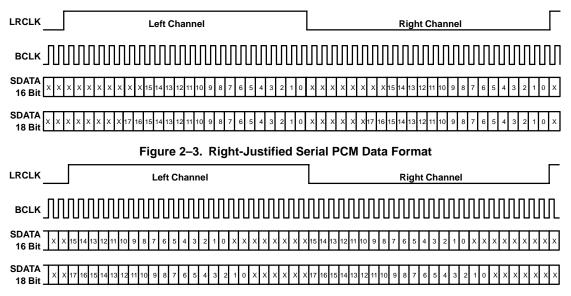

| 2–3    | Right-Justified Serial PCM Data Format                    | 2–4  |

| 2–4    | Left-Justified DSP Serial PCM Data Format (Inverted BCLK) | 2–4  |

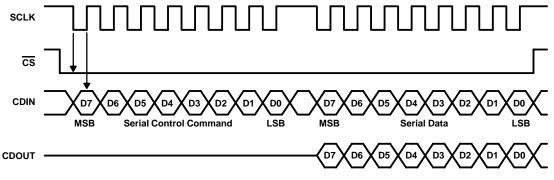

| 2–5    | Serial Interface Timing                                   | 2–10 |

| 3–1    | Serial Port Timing                                        | 3–6  |

| 3–2    | SPI Serial Control Port Timing                            | 3–6  |

| 4–1    | De-Emphasis 75 μs Low-Pass Filter at 2.12 kHz             | 4–1  |

| 4–2    | Application Schematic                                     | 4–2  |

# **List of Tables**

| Table | Title                                                                  | Page |

|-------|------------------------------------------------------------------------|------|

| 2–1   | Serial Port Signals                                                    | 2–3  |

| 2–2   | Control Register 00h Allowable Settings                                | 2–4  |

| 2–3   | Master Clock (MCLK) Rates Supported For Various Sample Rates (LRCLK) . | 2–5  |

| 4–1   | Digital Interface Capacitive Loading, $T_A = 25^{\circ}C$ ,            |      |

|       | $AV_{DD} = DV_{DD} = 5 V + 5\%$ , f <sub>s</sub> = 48 kHz              | 4–1  |

## 1 Introduction

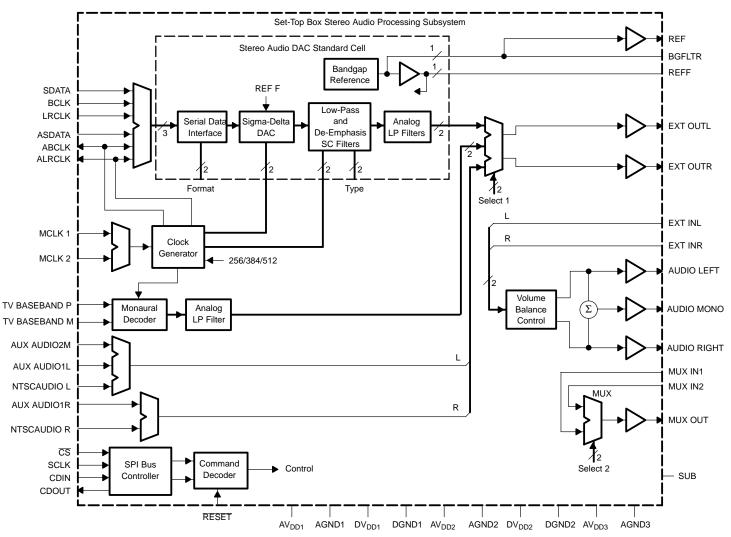

The TLC320AD80 is an audio processing subsystem designed to meet the audio needs of a broad range of set-top box applications. This device includes a high-performance stereo audio DAC, analog volume and balance control, analog TV monaural decoder, de-emphasis filter, and an analog wide-band multiplexer. The sigma-delta DAC performs data conversion with 85-dB performance. The architecture provides much flexibility, giving the user the option to use all or a subset of the functional blocks.

There are two serial digital interfaces for digital audio data and four analog audio inputs. The analog output of the device can be selected to be the output of the DAC, the output of the TV baseband filter, or pass-through of one of the analog inputs.

The digital interfaces enable ease of use by providing compatibility with the industry standard I<sup>2</sup>S digital audio port, and with the SPI<sup>™</sup> serial control interface. In addition, the digital audio interface supports additional interface protocols.

#### 1.1 Features

- Highly Integrated Analog Audio Functions

- Flexible Architecture Allows Variable Interconnects Between Functions

- Sigma-Delta DAC With 16-Bit Resolution and 82-dB Performance Typical

- Internal Monaural Decoder for TV Baseband Audio

- Four Analog Audio Inputs: Two Stereo and Two Mono

- Volume and Balance Control: 69 Step at 1 dB per Step With Mute

- Selectable 50/15 ms De-Emphasis Analog Filter

- Uncommitted Wide-Band Analog 2:1 Multiplexer

- Multiplexed Analog Output can Select the Output of the DAC or Analog Data Pass-Through From One of the Analog Audio Inputs

- Two Flexible Digital Serial Data Ports (Philips I<sup>2</sup>S Protocol, Left-Justified, and Right-Justified Formats)

- SPI Bus-Compatible Serial Control Port

- Sample Rates Supported in DAC: 8 kHz to 48 kHz

- Digital Serial Ports Support 16-Bit or 18-Bit PCM Digital Audio Data Format

- Analog Stereo Inputs can be Configured as Mono Inputs Through the Left Channel

- Analog Output With 600- $\Omega$  Load Drive and Short Circuit Protection

- Internal Voltage Reference

- TTL/CMOS Compatible

- Single 5-V Power Supply, 64-Pin TQFP Package

SPI<sup>™</sup> is a trademark of Motorola Inc.

### 1.2 Applications

- Direct Broadcast Satellite (DBS) Set-Top Boxes

- Digital Cable or Telco Set-Top Boxes

- High Definition Television (HDTV), Digital Audio Broadcast Receivers

- Video Laser Disks, Video CD, and CD-I Players

#### 1.3 Functional Block Diagram

1-3

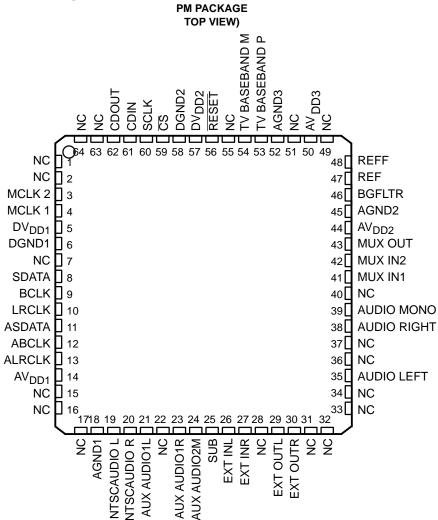

#### **1.4 Terminal Assignments**

1.5 Ordering Information

|                | PACKAGE              |

|----------------|----------------------|

| Τ <sub>Α</sub> | CHIP CARRIER<br>(PM) |

| 0°C to 70°C    | TLC320AD80CPM        |

## 1.6 Terminal Functions

| TERMINAL          |          | 1/0 |                                                                                                                                                                                                                                                  |  |  |

|-------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME              | NAME NO. |     | DESCRIPTION                                                                                                                                                                                                                                      |  |  |

| AGND1             | 18       | I   | Analog ground for sigma-delta DAC                                                                                                                                                                                                                |  |  |

| AGND2             | 45       | I   | Analog ground for analog audio output drivers                                                                                                                                                                                                    |  |  |

| AGND3             | 52       | I   | Analog ground for bandgap reference                                                                                                                                                                                                              |  |  |

| AUDIO LEFT        | 35       | 0   | Left channel line-level analog audio output. The AUDIO LEFT output driver provides line level signals (1 V <sub>rms</sub> max) for line output. The AUDIO LEFT output is capable of driving a 600- $\Omega$ load.                                |  |  |

| AUDIO MONO        | 39       | 0   | Monaural variable line-level analog audio output. The AUDIO MONO output signal is the sum of the AUDIO RIGHT and AUDIO LEFT outputs divided by 2. The output is capable of driving a $10$ -k $\Omega$ load.                                      |  |  |

| AUDIO RIGHT       | 38       | 0   | Right channel variable line-level analog audio output. The AUDIO RIGHT output driver provides line level signals (1 V <sub>rms</sub> max) for line output. The AUDIO RIGHT output is capable of driving a 600- $\Omega$ load.                    |  |  |

| AUX AUDIO1L       | 21       | I   | Left channel auxiliary analog audio input 1                                                                                                                                                                                                      |  |  |

| AUX AUDIO1R       | 23       | I   | Right channel auxiliary analog audio input 1                                                                                                                                                                                                     |  |  |

| AUX AUDIO2M       | 24       | I   | Mono channel auxiliary analog audio input 2                                                                                                                                                                                                      |  |  |

| ABCLK             | 12       | I/O | Auxiliary serial bit clock input. The ABCLK bit clock signal clocks the serial PCM data (ASDATA) into the TLC320AD80.                                                                                                                            |  |  |

| ALRCLK            | 13       | I/O | Auxiliary left/right channel indicator. ALRCLK signifies whether the serie<br>PCM data is associated with the left channel DAC or the right channel DAC                                                                                          |  |  |

| ASDATA            | 11       | I   | Auxiliary serial PCM data input port. ASDATA can be configured as 16 or 18 bits with the most significant bit (MSB) first, 2's complement format.                                                                                                |  |  |

| AVDD1             | 14       | I   | Analog 5-V power supply for the sigma-delta DAC                                                                                                                                                                                                  |  |  |

| AV <sub>DD2</sub> | 44       | I   | Analog 5-V power supply for the analog audio output drivers                                                                                                                                                                                      |  |  |

| AV <sub>DD3</sub> | 50       | Ι   | Analog 5-V power supply for the bandgap reference                                                                                                                                                                                                |  |  |

| BCLK              | 9        | I   | Serial bit clock input. BCLK clocks the serial PCM data (SDATA) into the device.                                                                                                                                                                 |  |  |

| BGFLTR            | 46       | I   | Bandgap reference filter. BGFLTR provides for noise filtering of the internal bandgap reference (2.25 V). BGFLTR requires a 0.1 $\mu$ F capacitor to analog ground. This voltage node should be loaded only with a high-impedance dc load.       |  |  |

| CDIN              | 61       | I   | SPI bus serial control data input. Data is transferred MSB first. CDII specifies the channel specific attenuation and mute, serial PCM data forma and rates, de-emphasis mode, audio input port selection, and stereo or monaural analog inputs. |  |  |

| CDOUT             | 62       | 0   | SPI bus serial control data output port                                                                                                                                                                                                          |  |  |

| CS                | 59       | I   | SPI bus chip select input (active low)                                                                                                                                                                                                           |  |  |

| DGND1             | 6        | I   | Digital ground for the sigma-delta DAC                                                                                                                                                                                                           |  |  |

| DGND2             | 58       | Ι   | Digital ground for the serial interface                                                                                                                                                                                                          |  |  |

| DV <sub>DD1</sub> | 5        | Ι   | Digital 5-V power supply for the sigma-delta DAC                                                                                                                                                                                                 |  |  |

| DV <sub>DD2</sub> | 57       | Ι   | Digital 5-V power supply for the serial interface                                                                                                                                                                                                |  |  |

| EXT INL           | 26       | Ι   | Left channel external analog audio input                                                                                                                                                                                                         |  |  |

| EXT INR           | 27       | I   | Right channel external analog audio input                                                                                                                                                                                                        |  |  |

## 1.6 Terminal Functions (Continued)

| TERMINAL      |     |     | DESCRIPTION                                                                                                                                                                                                                                                                                            |  |  |

|---------------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                            |  |  |

| EXT OUTL      | 29  | 0   | Left channel fixed line level analog audio output. The EXT OUTL output driver provides line level signals (1 $V_{rms}$ max) for line output. The EXT OUTL output is capable of driving a 10-k $\Omega$ load.                                                                                           |  |  |

| EXT OUTR      | 30  | 0   | Right channel fixed line level analog audio output. The EXT OUTR output driver provides line level signals (1 V <sub>rms</sub> max) for line output. The EXT OUTR output is capable of driving a 10-k $\Omega$ load.                                                                                   |  |  |

| LRCLK         | 10  | I   | Left/right channel indicator. LRCLK signifies whether the serial PCM data (SDATA) is associated with the left channel DAC or the right channel DAC.                                                                                                                                                    |  |  |

| MCLK 1        | 4   | I   | Master clock, sigma-delta DAC oversampling clock input. The TLC320AD80 defaults to MCLK 1. The TLC320AD80 can run off of MCLK 1 or MCLK 2.                                                                                                                                                             |  |  |

| MCLK 2        | 3   | I   | Auxiliary master clock, DAC oversampling clock input. The TLC320AD80 can run off of either MCLK 1 or MCLK 2.                                                                                                                                                                                           |  |  |

| MUX IN1       | 41  | I   | Wideband multiplexer input 1                                                                                                                                                                                                                                                                           |  |  |

| MUX IN2       | 42  | I   | Wideband multiplexer input 2                                                                                                                                                                                                                                                                           |  |  |

| MUX OUT       | 43  | 0   | Wideband multiplexer output. The multiplexer can output one of two in (MUX IN1, MUX IN2) or perform an audio mute. The MUX OUT outp capable of driving a $600-\Omega$ load.                                                                                                                            |  |  |

| NTSCAUDIO L   | 19  | I   | Left channel NTSC analog audio input                                                                                                                                                                                                                                                                   |  |  |

| NTSCAUDIO R   | 20  | I   | Right channel NTSC analog audio input                                                                                                                                                                                                                                                                  |  |  |

| REF           | 47  | I   | Voltage reference. The REF voltage provides a common mode reference 2.25 V for all audio output drivers. The REF voltage can also be used as external common mode reference with the restriction that only high-impedance dc load should be applied. REF should be bypassed w a 0.1 $\mu$ F capacitor. |  |  |

| REFF          | 48  | I   | Voltage reference filter. REFF is provided for low-pass filtering of the internal voltage reference (3.2 V) for the sigma-delta DAC. REFF should be bypassed with 10 $\mu$ F and 0.1 $\mu$ F capacitors. This voltage node should be loaded only with a high-impedance dc load.                        |  |  |

| RESET         | 56  | I   | Power down/reset. When $\overline{\text{RESET}}$ is held low, the TLC320AD80 is placed in a power-down state. The TLC320AD80 is reset on the rising edge of RESET.                                                                                                                                     |  |  |

| SCLK          | 60  | I   | SPI bus serial clock input. Control input data (CDIN) must be valid on the rising edge of SCLK. SCLK may be continuous or gated.                                                                                                                                                                       |  |  |

| SDATA         | 8   | I   | Serial PCM data input port. SDATA can be configured as 16 or 18 bits with the MSB first, 2s complement format.                                                                                                                                                                                         |  |  |

| SUB           | 25  | I   | Substrate ground connected to AGND plane.                                                                                                                                                                                                                                                              |  |  |

| TV BASEBAND P | 53  | I   | TV aural baseband multiplex noninverting input                                                                                                                                                                                                                                                         |  |  |

| TV BASEBAND M | 54  | Ι   | TV aural baseband multiplex inverting input                                                                                                                                                                                                                                                            |  |  |

## 2 Functional Description

The TLC320AD80 is an audio processing subsystem that includes a high-performance stereo audio DAC, analog volume and balance control, analog TV monaural decoder, de-emphasis filter, and an analog wide-band multiplexer. The sigma-delta DAC performs data conversion with 85-dB performance. The architecture provides much flexibility with the option to use all or some of the functional blocks.

The digital interfaces enable ease of use by providing compatibility with the industry standard  $I^2S$  digital audio port, and with the SPI serial control interface. The digital audio serial interface also supports additional interface protocols and 16-bit or 18-bit data formats.

The analog interface provides much flexibility. Four analog audio sources are supported including two stereo audio sources, a TV baseband audio signal, and one mono source. In addition, the inputs to the volume and balance and the wideband mux are external to the chip. This allows the option to connect intermediate analog functions between functional blocks. As a default, these connections should include dc blocking capacitors to eliminate analog offsets. Finally, the primary analog output of the device is provided by a multiplexer. This allows selection from one of the following sources: the DAC, the output of the monaural decoder, or pass-through of one of the analog inputs. The multiplexer also allows the two stereo inputs to be used as mono inputs. In this case, the left channel is routed into both the left and right outputs.

The TLC320AD80 integrates several audio functions into one device. Following is a brief description of the device. Subsections of this chapter describe the details. The functions include:

- Sigma-delta stereo DAC

- 50/15 ms de-emphasis analog filter

- Analog volume and analog balance control

- Output multiplexer to select between the various audio sources

- TV baseband monaural audio decoder

- Additional uncommitted 2:1 mono multiplexer

- Two flexible digital audio input ports

- A SPI compatible serial control interface

- Voltage reference with buffered output

The DAC audio input can be selected from either of the digital serial ports. Several sample rates are supported. In addition, a software-selectable 50/15  $\mu$ s de-emphasis filter is provided in the analog section of the DAC. The output of the DAC is fed into the output multiplexer. The aforementioned serial ports provide several timing protocols (Phillips I<sup>2</sup>S, left justified, right justified, DSP mode), each with 16-bit or 18-bit data formats.

The TV baseband monaural decoder receives differential audio inputs from two external terminals (TV BASEBAND P, TV BASEBAND M). The output of this decoder is fed into the output multiplexer. The decoder is a differential eighth order elliptic switched capacitor filter used to reject high frequency audio signals that may be present in the NTSC audio broadcast multiplex. Proper operation of this section requires that the master clock (MCLK) correspond to an audio sample rate of 32 kHz.

The analog volume and balance control receives inputs from external terminals. The output of this section provides independent stereo and mono outputs on three terminals. All three outputs are also short-circuit protected. The functionality of this block provides either ganged or individual gain control for the left and the right channel. There are 69 volume settings which range from 6 dB to -62 dB of gain in 1 dB/step increments.

The external connections to this function allow for dc blocking capacitors to be included on the board, thus eliminating dc offsets present on the source. A typical implementation would connect the output of the analog multiplexer (EXT OUTL, EXT OUTR) to the input of this function.

The analog output multiplexer allows selection of the several analog sources input to the device. One of these audio sources is the output of the DAC. The others are the output of the TV monaural decoder, either of the two stereo analog inputs, or auxiliary mono input. Mono sources are sent to both right and left channels. The output of this multiplexer provides stereo outputs on two terminals, each with 10 k $\Omega$  drive capability. Both terminals are short-circuit protected.

The master clock for the device is derived from an external clock source. Control register 01h selects MCLK 1, or MCLK 2 to be the master clock source. This clock is then used to clock the DAC, the digital audio serial ports, and the monural decoder, switched-capacitor filter. The serial ports can be selected independent form the MCLK 1 and MCLK 2 selection. However, the clock rate of the selected clock source partly determines the sampling rate of the device. Refer to Table 2–1, and the description of control register 00h.

The TLC320AD80 also provides an uncommitted 2:1 mono analog multiplexer. The inputs and outputs of this device are connected to external terminals.

The voltage reference is used internally for the analog sections of the device. The external terminals must be connected to decoupling capacitors. In addition, the reference terminals can be externally buffered for use with external support circuitry.

#### 2.1 Audio Input Ports

The audio inputs consist of: two digital serial interfaces, two stereo analog inputs, one analog TV baseband audio input, and one mono analog input. The TV baseband audio input is a differential input. All other analog inputs are single-ended.

The audio input is selected by programming control register 01h. Only one of these inputs is active at any one time. The others are disabled. That is, if an analog input is selected, then the digital serial interfaces are inactive.

The two digital serial interfaces provide the input to the DAC through a digital multiplexer. These interfaces support several serial protocols including I<sup>2</sup>S, left-justified, and right-justified formats. The data format is 16-bit or 18-bit precision, with MSB first. There is also a DSP-compatible mode available.

All single-ended analog inputs can be passed through to the main output of the device by means of an analog multiplexer. The differential TV baseband audio input (TV BASEBAND P, TV BASEBAND M) feeds a monaural decoder which then feeds the same multiplexer.

#### 2.1.1 Serial PCM Data Ports

The device includes two serial ports used to transfer digital audio data from an external digital source to the DAC: The AUX serial port (ASDATA, ABCLK, and ALRCLK) can be configured to operate in either master or slave mode. The main serial PCM port (SDATA, BCLK, and LRCLK) always operates in the slave mode. Note, that the only exclusion is that the AUX port does not support the DSP mode when configured as master.

Configuration of these serial ports is accomplished by means of the SPI-compatible control serial interface port. Specifically, the protocol (Philips I<sup>2</sup>S protocol, left-justified, right-justified, or DSP mode), and data format (16-bit or 18-bit) are selected by programming control register 00h. The multiplexer selection is programmed with control register 01h which will also enable or disable these serial data ports.

#### 2.1.1.1 Main Serial PCM Port

The main serial PCM (SDATA, BCLK, and LRCLK) port always operates in slave mode. That is, all clocks are inputs to the device. The LRCLK and BCLK clocks must be synchronous with MCLK.

A typical set-top-box application would connect this input to an MPEG/AC3 audio decoder.

#### 2.1.1.2 Aux Serial PCM Data Port

The aux serial port (ASDATA, ABCLK, and ALRCLK) operates in either the master or slave mode. The master mode supports all the documented interface protocols with the exception of the DSP mode. The slave mode supports all documented protocols without exception.

The aux serial PCM data port receives non-compressed data from an auxillary audio source. The slave mode is identical to the clock mode of main serial PCM port. In the master mode, this device generates the required BCLK and LRCLK clocks synchronously with the applied MCLK.

#### 2.1.1.3 Serial Interface Protocols Supported

The serial ports comprise the signals in Table 2–1.

| MAIN PORT | AUXILIARY PORT | DESCRIPTION                                                  |

|-----------|----------------|--------------------------------------------------------------|

| SDATA     | ASDATA         | PCM audio data. 16-bit or 18-bit data precision              |

| BCLK      | ABCLK          | Bit clock. Rate is equal to 32x, 48x, or 64x the sample rate |

| LRCLK     | ALRCLK         | Left/right clock. Rate is equal to the sample rate           |

#### Table 2–1. Serial Port Signals

Figure 2–1 through Figure 2–4 are for a bit clock (BCLK) set to  $48 \times$  the sample rate and 16-bit data precision. All serial protocols supported are shown.

| LRCLK                                                                | Left Channel                                            | Right Channel                                             |  |  |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| вс∟к∭                                                                |                                                         |                                                           |  |  |  |  |

| SDATA<br>16 Bit × ×                                                  | X 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 X X X X X X X X | X 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 X X X X X X X X X |  |  |  |  |

| SDATA<br>18 Bit × ×                                                  | X 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 X X X X X | X 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 X X X X X X |  |  |  |  |

| Figure 2–1. Philips I <sup>2</sup> S Protocol Serial PCM Data Format |                                                         |                                                           |  |  |  |  |

|                                                                      | Figure 2–1. Finis 1-3 Protocol                          | Serial PCW Data Format                                    |  |  |  |  |

|                                                                      | Left Channel                                            | Right Channel                                             |  |  |  |  |

|                                                                      | Left Channel                                            |                                                           |  |  |  |  |

|                                                                      |                                                         | Right Channel                                             |  |  |  |  |

#### Figure 2–4. Left-Justified DSP Serial PCM Data Format (Inverted BCLK)

| PRECISION | PRECISION MCLK BCLK DIVIDER JUSTIFICATION |     |    |                               |  |  |  |  |

|-----------|-------------------------------------------|-----|----|-------------------------------|--|--|--|--|

| 16-Bit    | 256×                                      | 64× | 4  | Left, right, I <sup>2</sup> S |  |  |  |  |

| 16-Bit    | 256×                                      | 32× | 8  | Left, right, <sup>I2</sup> S  |  |  |  |  |

| 16-Bit    | 384×                                      | 64× | 6  | Left, right, I <sup>2</sup> S |  |  |  |  |

| 16-Bit    | 384×                                      | 48× | 8  | Left, right, I <sup>2</sup> S |  |  |  |  |

| 16-Bit    | 384×                                      | 32× | 12 | Left, right, I <sup>2</sup> S |  |  |  |  |

| 16-Bit    | 512×                                      | 64× | 8  | Left, right, I <sup>2</sup> S |  |  |  |  |

| 16-Bit    | 512×                                      | 32× | 16 | Left, right, I <sup>2</sup> S |  |  |  |  |

| 16-Bit    | 256×                                      | 64× | 4  | Left, right, I <sup>2</sup> S |  |  |  |  |

| 18-Bit    | 384×                                      | 64× | 6  | Left, right, I <sup>2</sup> S |  |  |  |  |

| 18-Bit    | 384×                                      | 48× | 8  | Left, right, I <sup>2</sup> S |  |  |  |  |

| 18-Bit    | 512×                                      | 64× | 8  | Left, right, I <sup>2</sup> S |  |  |  |  |

#### Table 2–2. Control Register 00h Allowable Settings

| LRCLK (kHz) |                 | MCLK (MHz)      |                   |

|-------------|-----------------|-----------------|-------------------|

|             | 256 	imes LRCLK | 384 	imes LRCLK | 512 $	imes$ LRCLK |

| 48          | 12.288          | 18.432          | N/A               |

| 44.1        | 11.2896         | 16.9344         | N/A               |

| 32          | 8.192           | 12.288          | N/A               |

| 24          | 6.144           | 9.216           | N/A               |

| 22.05       | 5.6448          | 8.4672          | N/A               |

| 16          | N/A             | N/A             | 8.192             |

| 12          | N/A             | N/A             | 6.144             |

| 11.025      | N/A             | N/A             | 5.6448            |

| 8           | N/A             | N/A             | 4.096             |

#### Table 2–3. Master Clock (MCLK) Rates Supported For Various Sample Rates (LRCLK)

#### 2.1.2 Analog Audio Input Ports

The main analog audio input ports consist of two stereo audio inputs, one mono audio input, and one TV baseband audio input. The stereo inputs and the mono input can be passed through to the output (EXT OUTL, EXT OUTR) by means of the analog output multiplexer. The TV baseband audio is a differential input that feeds an internal monaural decoder before it is sent to the same output multiplexer.

The secondary analog audio inputs consist of one stereo input to the volume and balance control and two mono inputs to the wideband multiplexer. These inputs are intended primarily for interconnecting functional blocks by means of dc blocking capacitors. However, it also provides the user with the ability to combine internal functions with additional external analog functions. All inputs should be connected through dc-blocking capacitors.

#### 2.1.2.1 Stereo Analog Input Ports

The two stereo audio input ports (NTSCAUDIO L, NTSCAUDIO R, AUX AUDIO1L, AUX AUDIO1R) are single-ended inputs. These inputs are sent to the output multiplexer without additional analog processing. The output of the multiplexer can be externally connected to another functional block such as the volume and balance control. These stereo inputs also have the ability to function in mono mode. In this mode, the left channel of the selected input is sent to both the left and right outputs (EXT OUTL, EXT OUTR). Control register 01h is used to program the mono or stereo mode for these inputs.

A typical application would connect the NTSC audio input to the output of a MTS stereo decoder. The AUX AUDIO1 port would be connected to an alternate nonbroadcast audio source.

#### 2.1.2.2 Mono Analog Input Port

The one mono audio port (AUX MONO 2M) is a single-ended input. This input is sent to the output multiplexer without additional analog processing. However, the output of the multiplexer can be externally connected to another functional block such as the volume and balance control. This input is internally applied to both the left and right audio channels.

A typical application would connect the AUX MONO 2M input to receive the second audio program (SAP) channel output of an MTS stereo decoder.

#### 2.1.2.3 TV Audio Baseband Input

The TV baseband audio audio port (TV BASEBAND P, TV BASEBAND M) is a mono differential input. This input feeds an internal a monaural decoder used to extract the mono (left and right) signal from the TV baseband. The output of the monaural decoder is sent to the output multiplexer.

The monaural decoder is a differential, eighth-order switched-capacitor filter. Proper operation requires that the master clock (MCLK 1 or MCLK 2) and control register settings correspond to a sample rate of 32 kHz. These settings ensure the filter requirements for proper stopband rejection. The purpose of the filter is to reject specific signals from the NTSC audio broadcast multiplex. The signals rejected include the 15.73425 kHz BTSC stereo pilot tone, left and right stereo subcarriers, SAP channel, Pro channel, and data channel as allowed by the FCC.

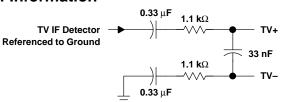

A typical connection would connect this input to the output of a TV IF detector. Therefore, composite TV aural baseband signal would be demodulated by the TV analog IF detector (without an MTS stereo decoder) and then input to the TLC320AD80.

A passive single pole low-pass filter with a 3-dB bandwidth of 2.12 kHz should be connected to the TV baseband differential input to provide the required 75  $\mu$ s de-emphasis filter. This external filter also acts as an anti-aliasing filter for the internal switched capacitor monaural decoder.

#### 2.1.2.4 Volume and Balance External Analog Input

This stereo audio input (EXT INL, EXT INR) is primarily intended to receive the external stereo audio output (EXT OUTL, EXT OUTR) of the TLC320AD80. However, the user has the option to connect additional analog functions in between these ports. The input should be ac-coupled to remove dc offsets that may be present in the incoming signal.

The input resistance of this port varies as a function of the volume control setting. The input resistance is lowest ( $\ge 20 \text{ k}\Omega$ ) when the volume control is at its maximum setting of 6 dB. The input resistance is reduced to approximately 2 k $\Omega$  when the capacitor precharge mode is selected from control register 01h. The capacitor precharge mode is provided to charge and discharge the external ac coupling capacitor quickly, overriding the input resistance of the volume control setting.

#### 2.1.2.5 Wideband Multiplexer Analog Inputs

The MUX IN1 and MUX IN2 signals are the analog inputs to an uncommitted wideband multiplexer. A typical application would use this multiplexer to provide source selection for the input to a channel 3/4 RF modulator.

#### 2.1.3 Audio Source Selection Procedure

Changing the audio source selection between any two of the six audio inputs can produce an audible click depending on the difference between the corresponding signal values at the time of switching. This difference between signals could be as large as 2.8 V peak-to-peak which would produce a very loud audible click. This audible click can be eliminated on the variable audio outputs (AUDIO RIGHT, AUDIO LEFT, and AUDIO MONO) by using the zero crossing mute function in conjunction with source selection changes. This procedure will not eliminate audible clicks on the fixed audio outputs (EXT OUTR, EXT OUTL) since the zero crossing mute function is located in the volume control block.

Prior to each audio source selection change, the audio output should be muted by writing 00h to volume control register 03h. The output signal follows the currently selected audio input until the next zero crossing occurs which activates the mute. After a recommended time delay of 4096 LRCLK cycles, the audio source can be changed by writing to control register 01h. The capacitor precharge mode and the audio input port mute should also be enabled by setting bit D1 to 1 and clearing bit D0 to 0 of control register 01h. After a second recommended time delay of 512 LRCLK cycles, the precharge mode and audio input port mute should be disabled and then the audio can be unmuted by restoring the original volume control setting to control registers 03h and 04h. The output signal remains muted until the next zero crossing occurs and then follows the newly selected audio input. The second delay time of 512 LRCLK cycles is required to allow

enough time for the voltage across the capacitors connecting the external stereo output to the external stereo input to reach a steady state condition.

A similar approach is required to prevent audible clicks on the output of the wideband multiplexer. Prior to each multiplexer input selection change, the multiplexer output should be muted by clearing bit D5 to 0 of control register 02h. The output signal follows the currently selected multiplexer input until the next zero crossing occurs which activates the mute. After a recommended time delay of 4096 LRCLK cycles, the multiplexer input selection can be changed by writing to bit D2 of control register 01h. The multiplexer output can then be unmuted by setting bit D5 to 1 of control register 02h. The output signal remains muted until the next zero crossing occurs and then follows the newly selected multiplexer input.

#### 2.1.4 Audio Input Port Mute and Capacitor Precharge Mode

The sigma-delta DAC and the monaural decoder may introduce offset errors that could cause audible clicks or pops to occur during volume control changes. To prevent this audible noise, the external audio output (EXT OUTL, EXT OUTR) should be connected to the external audio inputs (EXT INL, EXT INR) through ac coupling capacitors to remove this offset error.

During source selection changes, sufficient time needs to be provided to allow the voltage across these external capacitors to reach a steady state condition before returning the audio to an unmuted condition. In order to minimize this required settling time, the input resistance of the external audio inputs can be reduce by a factor of 10 by selecting the capacitor precharge mode. The input resistance of this port normally varies as a function of the volume control setting. The input resistance is lowest ( $\geq 20 \text{ k}\Omega$ ) when the volume control is at its maximum setting of 6 dB. When the capacitor precharge mode is selected by setting control register 01h to 1, the input resistance is reduced to approximately 2 k $\Omega$ .

The audio input port mute should be enabled when using the capacitor precharge mode by clearing bit D0 of control register 01h to 0. When the audio input port mute is enabled, the serial PCM audio data is disabled (forced to 0) at the input to the sigma-delta DAC, the differential input to the monaural decoder is shorted, and the remaining analog audio inputs are muted. This removes the signal content but not the offset error of a particular audio channel which is necessary in the capacitor precharge mode since the time constant may be insufficient to find the long term average of the selected audio signal.

The audio input port mute feature may also be used in conjunction with the volume control mute to provide increased audio mute attenuation for the serial PCM audio inputs. This improved mute attenuation occurs following 30 LRCLK cycles when the 0 input data propagates to the output of the sigma-delta DAC. The serial PCM audio data is enabled and disabled at the beginning of an audio sample period (rising edge of LRCLK) for an audio input port mute or unmute operation. The serial PCM data must be re-enabled prior to requesting an unmuted volume control setting to provide the audio signal necessary to perform a zero crossing unmute at the volume control stage.

#### 2.2 Analog Audio Outputs

The TLC320AD80 analog outputs consist of two stereo outputs and two mono outputs. All are single-ended analog outputs.

#### 2.2.1 Variable Stereo Audio Outputs

The variable stereo audio output (AUDIO LEFT, AUDIO RIGHT) provides the output of the volume and balance functional block. This output is intended as the final output of the TLC320AD80. In addition, one of the mono outputs (AUDIO MONO) is derived from this stereo audio pair. The AUDIO MONO output is the summation of the AUDIO LEFT and AUDIO RIGHT channels divided by 2.

The variable stereo audio output (AUDIO LEFT, AUDIO RIGHT) provides the selected audio input after application of the volume control. The full-scale analog output of each channel is typically 2.8 V peak-to-peak. These analog outputs can drive load impedances as low as 600  $\Omega$  and are short circuit protected to 10 mA.

A typical set-top-box application would connect AUDIO MONO output to one of the inputs of the wideband multiplexer after applying external 75  $\mu$ s pre-emphasis. If selected by the wideband multiplexer, the monaural audio output would then be processed by the channel 3/4 RF modulator and then connected to an external TV or VCR receiver (with a coaxial cable). The full-scale analog output is typically 2.8 V peak-to-peak. This analog output (AUDIO MONO) can drive load impedances as low as 10 k $\Omega$  and is short circuit protected to 7 mA.

#### 2.2.2 External Stereo Audio Output

The external stereo output (EXT OUTL, EXT OUTR) provides the output of the analog multiplexer (connected to the analog inputs, the DAC, and the monaural decoder). A typical connection would ac couple this output to the volume and balance external inputs. Alternate connections may include external analog functions located before the volume and balance input.

The selected audio input is output at a fixed volume of 0 dB on the external stereo audio output (EXT OUTL, EXT OUTR). The full-scale analog output of each channel is typically 2.8 V peak-to-peak. The analog outputs can drive load impedances as low as 10 k $\Omega$  and are short circuit protected to 7 mA.

#### 2.2.3 Wideband Multiplexer Output

The wideband multiplexer output is a single-ended output provided by the wide-band multiplexer. The inputs and output of this multiplexer are provided by external terminals. A typical application would use this function to provide source selection for a channel 3/4 RF modulator. The modulator would then be connected to a TV or VCR by means of a coaxial cable.

The wideband multiplexer can output one of two inputs (MUX IN1 AND MUX IN2) or perform an audio mute. A typical connection would connect one input to the composite TV baseband audio signal. The other input would connect to the AUDIO MONO output of the TLC320AD80 with external 75  $\mu$ s pre-emphasis. This feature allows remodulating an analog audio program which was broadcast in stereo without sacrificing the stereo content.

The wideband multiplexer has a 3-dB bandwidth greater than 90 kHz to provide a flat response for the SAP channel of a TV aural baseband signal. The volume control mute does not have any effect on the wideband multiplexer output. The wideband multiplexer has an independent mute control located at bit D5 of control register 02h. The full-scale analog output is typically 2.8 V peak-to-peak. The analog output can drive load impedances as low as 600  $\Omega$  and is short circuit protected to 10 mA.

#### 2.3 Volume/Balance/Mute Control

The inputs and outputs of the volume and balance control are provided by external terminals. The inputs to this block (EXT INL, EXT INR) are typically ac-coupled to the EXT OUTL and EXT OUTR outputs. The outputs consist of a stereo pair (AUDIO LEFT, AUDIO RIGHT) and a mono output (AUDIO MONO). The volume of the left and right audio channels can be controlled independently for stereo balance control. The lowest volume control setting corresponds to audio mute.

#### 2.3.1 Volume Control

The TLC320AD80 provides a volume control range from 6 dB to -62 dB in 1 dB increments. Volume changes can be executed in each channel (left or right) independently or in ganged mode. All volume transitions take effect at zero-crossing to avoid clicks during volume transitions.

Volume control changes are programmed by means of control registers 03h and 04h (see *Appendix A*, *Register Set*). These changes will take effect during zero crossing of the data on a given channel. A zero crossing is defined by when the relative magnitude of the signal is zero (i.e., equal to the V<sub>ref</sub> voltage level). However, if no zero crossing occurs within 4096 LRCLK periods, the gain is forced to change. Independent left channel and right channel zero crossing detectors are provided to minimize pops or clicks on stereo signals.

The time-out feature of 4096 LRCLK periods can be eliminated by setting D7 of control register 04h, in which case the data values must have a zero crossing for the next gain setting to be sent to the amplifier. This feature is useful in applications where severe data latency is either expected or needed and an audio pop is to be avoided. Many other multimedia applications such as acoustic echo cancellation will benefit from this feature.

The 70th volume control setting corresponds to audio mute. Mute provides greater than 80 dB of attenuation from a full-scale audio output.

It is possible for an audible click or pop to occur immediately after a zero crossing unmute. If an audio amplifier needs to slew rate limit immediately after being unmuted to catch up with a rapidly changing audio input, then that amplifier may subsequently overshoot causing an audible click or pop. By utilizing the programmable volume control feature of the TLC320AD80, a soft mute function can be implemented in software that eliminates this potential cause of audible noise. A soft mute would provide a gradual attenuation change over an appropriate time interval when entering a muted condition rather than an allowing an abrupt change to occur. The original volume control setting would be gradually restored upon leaving a muted condition.

#### 2.4 Sigma-Delta DAC

The sigma-delta DAC contains an interpolation filter and single bit modulator with 64 times oversampling. The switched-capacitor and continuous time analog filter which follows, provides the smoothed analog signal output.

#### 2.4.1 Interpolator / Modulator

The interpolation filter receives 16-bit or 18-bit data at the sample rate and interpolates new values at a rate of 64-times the sample rate. These values are provided to the sigma-delta modulator for noise shaping. The output of the digital modulator is a one bit data stream which is sent to a switched capacitor filter.

#### 2.4.2 Continuous Time and Switched Capacitor Filters

The switched capacitor filter performs the low-pass filter function. The filter characteristics are stated in the specification section. The corner frequency of this filter is directly proportional to the selected sample rate. The continuous time filter is used to reduce the switching frequency energy of the switched capacitor filter, and any remaining high frequency energy. This switched-capacitor filter also provides the selectable 50/15  $\mu$ s de-emphasis under control of register 02h.

#### 2.5 Serial Control Port

The SPI-compatible serial port controls all the programmable states of the TLC320AD80. The 4-wire SPI compatible interface is composed of a serial clock (SCLK), an active low chip select  $\overline{(CS)}$ , a command data input (CDIN), and a command data output (CDOUT). There are five 8-bit control registers within the TLC320AD80.

#### 2.5.1 Serial Control Port Description

The serial control port is activated when the active low CS signal is asserted. The CS input must be asserted low prior to a data transfer and must remain low for the duration of the transfer as shown in Figure 2–5.

The serial command data input (CDIN) is sampled with the rising edge of SCLK. The CDIN data is MSB first and unsigned.

While the  $\overline{CS}$  input is low, the <u>SCLK</u> input must idle high when there is no valid data to be transferred. The first byte of CDIN data after  $\overline{CS}$  activation is the serial control command. The serial control command includes a 4-bit control register address [D(3–0)] and a control port direction bit (D7). The second byte of data is the register data.

The  $\overline{CS}$  input must make a low to high transition in order to specify a new control register address. When the  $\overline{CS}$  input is set to 1, the serial command data output (CDOUT) is placed in a high-impedance state. When the CS input is cleared to 0, the CDOUT output is held low during nonvalid data intervals.

The serial control port is activated when the  $\overline{CS}$  signal (active low) goes low. The  $\overline{CS}$  line must be low prior to data transactions and must remain low for the duration of the transaction. The serial command data input (CDIN) is sampled on the rising edge of SCLK. The CDIN data is MSB first and unsigned. While the  $\overline{CS}$  input is low, the <u>SCLK</u> input must idle high when there is no valid data to be transferred. The first byte of CDIN data after  $\overline{CS}$  activation is set up as a serial control command. The serial control command includes a 4-bit control register address [D(3–0)] and a control port direction bit (D7). The second byte of data is set up as control register data. The  $\overline{CS}$  input must make a low-to-high transition in order to specify a new control register address. When the  $\overline{CS}$  input goes low, the CDOUT output is held low during nonvalid data intervals.

Figure 2–5. Serial Interface Timing

#### 2.5.2 Serial Control Command Format

The serial control command format is shown below.

| D7 | D6 | D5     | D4 | D3 | D2   | D1    | D0 |

|----|----|--------|----|----|------|-------|----|

| WR |    | Unused |    |    | ADDR | (3–0) |    |

The serial control command fields are defined as:

WR – Serial interface direction

When this bit is 1:

- The serial interface is in write mode.

- Serial data is sent control register specified in the serial control command

When this bit is 0:

- The serial interface is in read mode.

- The control register data is output to CDOUT according to the control register address.

ADDR(3-0) - Control register address specifies the TLC320AD80 register being accessed.

#### 2.5.3 Power-Down/Reset

When the RESET terminal is held low, the TLC320AD80C is put in a power-down condition. During power down, the sigma-delta DACs are disabled to conserve power and the digital output drivers (ABCLK, ALRCLK, and CDOUT) are placed in a high-impedance state. When powered down, the analog audio outputs settle near  $V_{ref}$  (2.25 V).

There are two ways in which to initialize the TLC320AD80C.

- The TLC320AD80C begins reset and initialization on the rising edge of the RESET signal. A stable clock waveform having a frequency within the specified allowable frequency range (see Timing Requirements section) must be present at the master clock (MCLK1) input prior to the rising edge of the RESET signal for proper operation. In order to prevent the occurrence of audible pops or clicks from the TLC320AD80C, the RESET terminal must be kept low 500 ms after the power supplies have settled. This provides adequate time for the 2.25-V based line outputs to charge the large output capacitors on the analog audio outputs while minimizing any audible pops.

- Set bit D0 of control register 02h to 1.

To maximize the initialization cycle accuracy, the TLC320AD80C should not be continually polled. This initialization cycle takes about 500 ms to complete following the rising edge of RESET.

The power-down mode can also be selected by setting bit D0 of control register 02h to 1. In this software controlled power-down mode the sigma-delta DACs, the monaural decoder, and the audio input amplifiers are all disabled to conserve power. The external audio outputs (EXT OUTR, EXT OUTL) are muted to hold the output voltage at  $V_{ref}$ . Since muting the external audio output can cause an audible click, a zero crossing mute should be performed prior to initiating a software power-down.

#### 2.6 Software Interface

Control of the TLC320AD80 is accomplished by means of the SPI serial interface and the control registers described in Appendix A.

### **3** Specifications

# 3.1 Absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, AV <sub>DD</sub> (see Note 1)  | –0.3 V to 6 V                                                             |

|------------------------------------------------------|---------------------------------------------------------------------------|

| Supply voltage range, DV <sub>DD</sub> (see Note 2)  | 0.3 V to 6 V                                                              |

| Analog input voltage                                 | $\dots \dots -0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$                   |

| Digital input voltage                                | $\dots \dots -0.3 \text{ V to } \text{DV}_{\text{DD}}^{} + 0.3 \text{ V}$ |

| Operating free-air temperature range, T <sub>A</sub> | 0°C to 70°C                                                               |

| Storage temperature range                            | –65°C to 150°C                                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. Voltage values for maximum ratings are with respect to AGND.

- 2. Voltage values for maximum ratings are with respect to DGND.

#### 3.2 Recommended Operating Conditions

|                                                      | MIN  | NOM | MAX  | UNITS |

|------------------------------------------------------|------|-----|------|-------|

| Analog supply voltage, AV <sub>DD</sub> (see Note 3) | 4.75 | 5   | 5.25 | V     |

| Digital supply voltage, DV <sub>DD</sub>             | 4.75 | 5   | 5.25 | V     |

| Operating free-air temperature, T <sub>A</sub>       | 0    |     | 70   | °C    |

| Storage temperature, T <sub>Stg</sub>                | -65  |     | 150  | °C    |

NOTE 3: Voltages at analog inputs and outputs and V<sub>CC</sub> are with respect to the AGND terminal.

#### 3.2.1 Static Digital Specifications, $T_A = 25^{\circ}C$ , $AV_{DD} = DV_{DD} = 5 V + 5\%$

|                                            | TEST CONDITIONS        | MIN | NOM | MAX  | UNITS |

|--------------------------------------------|------------------------|-----|-----|------|-------|

| High-level input voltage, V <sub>IH</sub>  |                        |     |     | 2    | V     |

| Low-level input voltage, VIL               |                        | 0.8 |     |      | V     |

| High-level output voltage, V <sub>OH</sub> | I <sub>O</sub> = -1 mA | 2.4 |     | DVDD | V     |

| Low-level output voltage, VOL              | $I_{O} = 4 \text{ mA}$ |     |     | 0.4  | V     |

| Input leakage current                      |                        | -10 |     | 10   | μA    |

| Output leakage current                     |                        | -10 |     | 10   | μA    |

| Leakage current, digital I/O terminals     | Input mode             | -10 |     | 10   | μΑ    |

|                                   | 00              |     |     |     |       |

|-----------------------------------|-----------------|-----|-----|-----|-------|

|                                   | TEST CONDITIONS | MIN | NOM | MAX | UNITS |

| Power supply current (see Note 4) | Normal          |     | 52  | 90  | mA    |

| Power supply current (see Note 4) | Power-down mode |     | 19  |     | mA    |

| Rewar supply rejection            | 1 kHz           |     | 40  |     | dB    |

| Power supply rejection            | 1 MHz           |     | 30  |     | dB    |

#### 3.2.2 Power Supplies, $T_A = 25^{\circ}C$ , $AV_{DD} = DV_{DD} = 5 V + 5\%$

NOTE 4: Power supply current rating for line outputs driving 10-k $\Omega$  load.

#### 3.3 Electrical Characteristics

#### 3.3.1 Analog Audio Channel Performance, T<sub>A</sub> = 25 °C, AV<sub>DD</sub> = DV<sub>DD</sub> = 5 V $\pm$ 5%

|                                 |             | · <b>n</b> ·                                                                                                                            | 00   | 00   |       |         |

|---------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|---------|

| PARA                            | METER       | TEST CONDITIONS                                                                                                                         | MIN  | TYP  | MAX   | UNITS   |

| Full-scale input voltage        |             | All analog audio inputs                                                                                                                 | 2.66 | 2.8  | 2.94  | VPP     |

| Common mode input vo            | Itage       | All analog audio inputs                                                                                                                 | 2.1  | 2.25 | 2.4   | V       |

| Inputimpodopoo                  | Resistance  | All analog audio inputs                                                                                                                 | 20   |      |       | kΩ      |

| Input impedance                 | Capacitance | All analog audio inputs                                                                                                                 |      | 15   |       | pF      |

| 3-dB Bandwidth                  |             | All analog audio inputs<br>except the TV<br>BASEBAND P or TV<br>BASEBAND M inputs                                                       | 20   |      |       | kHz     |

| Signal-to-noise ratio (SN       | IR)         | A-weighted, referenced<br>to 0-dB f <sub>S</sub> ,<br>All analog audio inputs<br>except the TV<br>BASEBAND P or TV<br>BASEBAND M inputs | 80   | 85   |       | dB      |

| Total harmonic distortion (THD) |             | A-weighted, referenced to 0-dB f <sub>S</sub>                                                                                           |      |      | 0.02% |         |

| Frequency response              |             | 20 Hz to 20 kHz                                                                                                                         | -0.8 |      | 0.2   | dB      |

| Deviation from linear pha       | ase         | 20 Hz to 20 kHz                                                                                                                         |      | ±1.5 |       | degrees |

# 3.3.2 Volume Control and Output Drivers Performance, $T_A$ = 25°C, $AV_{DD}$ = $DV_{DD}$ = 5 V $\pm$ 5%

|      | PARAMET                  | ER                         | TEST CONDITIONS                                                        | MIN  | TYP  | MAX  | UNITS           |

|------|--------------------------|----------------------------|------------------------------------------------------------------------|------|------|------|-----------------|

|      |                          | Range                      | Total continuous control range                                         |      | 68   |      | dB              |

|      |                          | Step resolution            | Differential error                                                     | 0.5  | 1    | 1.5  | dB              |

|      | Volume control           | Volume integral error      | Deviation from ideal volume setting                                    |      | ±2   |      | dB              |

|      |                          | Gain tracking              | Left and right channel gain matching                                   |      | ±1   |      | dB              |

|      |                          | Mute<br>attenuation        | Relative to volume setting of 0 dB                                     | -80  | -90  |      | dB              |

|      | Full-scale output        | voltage                    | All analog audio outputs, maximum volume                               | 2.66 | 2.8  | 2.94 | V <sub>PP</sub> |

|      | Common mode or           | utput voltage              | All analog audio outputs                                               | 2.1  | 2.25 | 2.4  | V               |

|      | Output resistance        | (open loop)                | All analog audio outputs                                               |      | 300  |      | Ω               |

|      |                          | Oursetland                 | Short circuit protected, AUDIO<br>RIGHT, AUDIO LEFT, MUX OUT           | 600  |      |      | Ω               |

|      | Output drive             | Ouput load<br>resistance   | Short circuit protected, AUDIO<br>MONO, EXT OUTR,<br>EXT OUTL          | 10   |      |      | kΩ              |

|      | capability               | Oursutlaad                 | Short circuit protected, AUDIO<br>RIGHT, AUDIO LEFT                    |      |      | 300  | pF              |

|      |                          | MO                         | Short circuit protected, AUDIO<br>MONO, EXT OUTR,<br>EXT OUTL, MUX OUT |      |      | 100  | pF              |

| Vref | Output reference         | voltage                    |                                                                        | 2.1  | 2.25 | 2.4  | V               |

|      | Output reference current |                            |                                                                        |      | 100  |      | μA              |

|      | Audio channel separation | EXT OUTL,<br>EXT OUTR      |                                                                        |      | 80   |      | dB              |

|      | (relative to 0 dB)       | AUDIO LEFT,<br>AUDIO RIGHT |                                                                        |      | 80   |      | dB              |

# 3.3.3 Monaural Decoder Performance, T\_A = 25°C, AV\_{DD} = DV\_{DD} = 5 V $\pm$ 5%, f\_s = 32 kHz

| PARA                        | METER              | TEST CONDITIONS                                                                          | MIN      | TYP  | MAX | UNITS |

|-----------------------------|--------------------|------------------------------------------------------------------------------------------|----------|------|-----|-------|

| 3-dB Bandwidth              |                    | TV BASEBAND P or TV<br>BASEBAND M inputs only,<br>MCLK = 256 x 32 kHz or<br>384 x 32 kHz |          | 14   |     | kHz   |

| Signal-to-noise ratio (SNR) |                    | A-weighted,<br>referenced to $-3 \text{ dB}$ ,<br>$f_S = 50 \text{ Hz}$ to 14 kHz        |          | 54   |     | dB    |

| Total harmonic disto        | ortion (THD)       | A-weighted,<br>referenced to –3 dB,<br>f <sub>S</sub> = 50 Hz to 14 kHz                  |          | 50   |     | dB    |

|                             | -3-dB Passband     |                                                                                          | 14       |      |     | kHz   |

| BTSC filter                 | Passband ripple    | TV baseband input filter                                                                 |          | ±0.5 |     | dB    |

| DISC III.el                 | Stopband           | referenced to 0 dB                                                                       | 15.73425 |      |     | kHz   |

|                             | Stopband rejection |                                                                                          | -44      | -50  |     | dB    |

| PARAMETER                       | TEST CONDITIONS                                         | MIN | TYP   | MAX  | UNITS   |

|---------------------------------|---------------------------------------------------------|-----|-------|------|---------|

| 3-dB Bandwidth                  | MUX IN1 or MUX IN2 inputs                               | 90  |       |      | kHz     |

| Signal-to-noise ratio (SNR)     | Unweighted, referenced to 0 dB, $f_S = 50$ Hz to 47 kHz | 70  | 85    |      | dB      |

| Total harmonic distortion (THD) | Unweighted, referenced to 0 dB, $f_S = 50$ Hz to 47 kHz |     |       | 0.1% |         |

| Frequency response              | 50 Hz to 47 kHz                                         |     | ±0.35 |      | dB      |

| Deviation from linear phase     | 50 Hz to 47 kHz                                         |     | ±2    |      | degrees |

3.3.4 Wideband Multiplexer Performance,  $T_A = 25^{\circ}C$ ,  $AV_{DD} = DV_{DD} = 5 V \pm 5\%$

# 3.3.5 PCM Audio Channel Performance, $T_A$ = 25°C, $AV_{DD}$ = $DV_{DD}$ = 5 V $\pm$ 5%, $f_S$ = 48 kHz

| PAR                                  | AMETER              | TEST CONDITIONS                                               | MIN  | TYP   | MAX | UNITS   |